- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385408 > HT95C20P (Holtek Semiconductor Inc.) 8-Bit CID Type Phone Controller MCU PDF資料下載

參數(shù)資料

| 型號: | HT95C20P |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit CID Type Phone Controller MCU |

| 中文描述: | 8位偵緝型電話MCU控制器 |

| 文件頁數(shù): | 32/50頁 |

| 文件大?。?/td> | 324K |

| 代理商: | HT95C20P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

HT95C200/20P/300/30P

Rev. 0.10

32

October 1, 2002

Preliminary

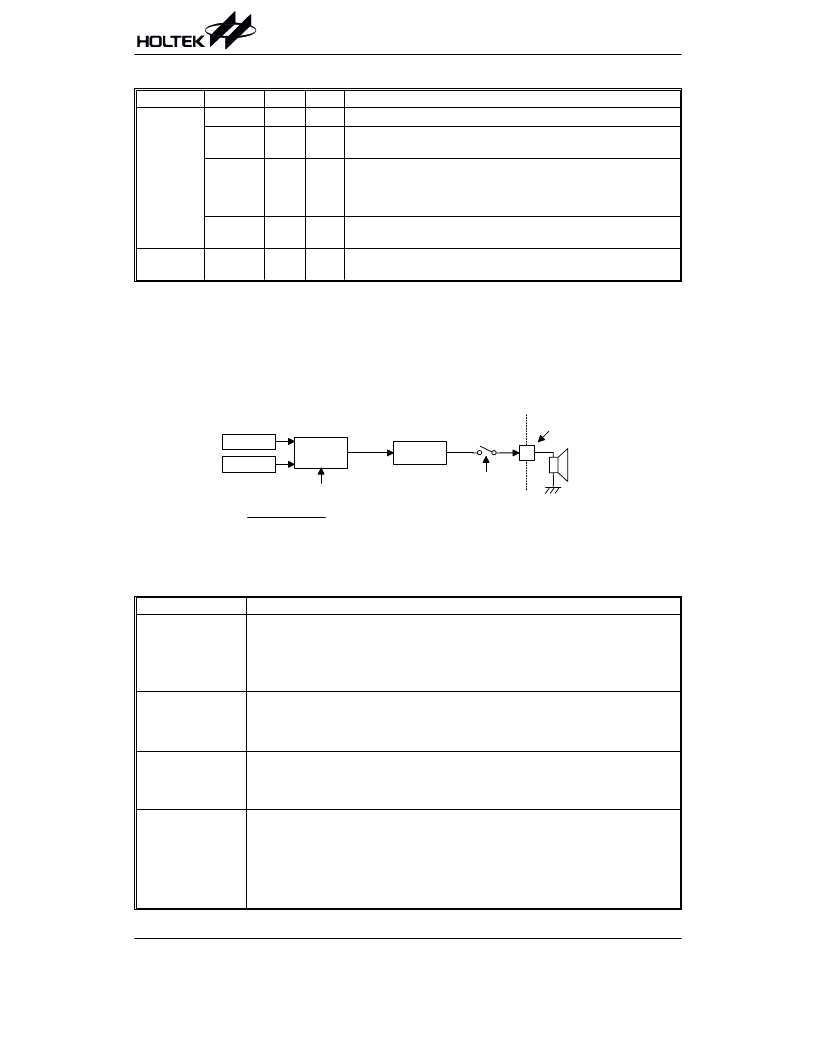

PFD generator

Register

Label

Bits

R/W

Function

PFDC

(2EH)

3~0

RO

Unused bit, read as 0

PFDEN

4

RW

1: Enable PFD output

0: Disable PFD output, the MUSIC pin output low level.

PRES0

PRES1

5

6

RW

Bit6, 5=00: Prescaler output= PFD frequency source/1

Bit6, 5=01: Prescaler output= PFD frequency source/2

Bit6, 5=10: Prescaler output= PFD frequency source/4

Bit6, 5=11: Prescaler output= PFD frequency source/8

FPFD

7

RW

1: The PFD frequency source is 3.58MHz/4

0: The PFD frequency source is 32768Hz

PFDD

(2FH)

7~0

RW

PFD data register

The PFD (programmable frequency divider) is implemented in the phone controller. It is composed of two portions: a

prescaler and a general counter.

The prescaler is controlled by the register bits, PRES0 and PRES1. The general counter is programmed by an 8-bit

register PFDD.

The source for this generator can be selected from 3.58MHz/4 or 32768Hz. To enable the PFD output, write 1 to the

PFDEN bit.

The PFDD is inhibited to write while the PFD is disabled. To modify the PFDD contents, the PFD must be enabled.

When the generator is disabled, the PFDD is cleared by hardware.

PFD output frequency=Prescaler output

2

(N

1)

, where N=the value of the PFDD

Mask option table

The following shows many kinds of mask options in the telephone controller. All these options should be defined in or-

der to ensure proper system functions.

Name

Mask Option

WDT

WDT source selection

RC

Select the WDT OSC to be the WDT source.

T1

Select the instruction clock to be the WDT source.

32kHz

Select the external 32768Hz to be the WDT source.

Disable

Disable WDT function.

WDTinstr

This option defines how to clear the WDT by instruction.

One clear instruction

The CLR WDT can clear the WDT.

Two clear instructions

Only when both of the CLR WDT1 and CLR WDT2 have been

executed, then WDT can be cleared.

Wake-up PA

Port A wake-up selection.

Define the activity of wake-up function.

All port A have the capability to wake-up the chip from a HALT.

This wake-up function is selected per bit.

Pull-high Port A

Pull-high Port B

Pull-high Port D

Pull-high Port E

Pull-high option.

This option determines whether the pull-high resistance is viable or not.

Port A pull-high option is selected per bit.

Port B pull-high option is selected per bit.

Port D pull-high option is selected per nibble for HT95C300/30P.

Port D pull-high option is selected per byte for HT95C200/20P.

Port E pull-high option is selected per nibble.

8

8

<

;

- "

;

'

& 0 2 . + 5 6

& % +

5 6 ( *

<

;

<

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT95C300 | 8-Bit CID Type Phone Controller MCU |

| HT95C30P | 8-Bit CID Type Phone Controller MCU |

| HT95C200 | 8-Bit CID Type Phone Controller MCU |

| HT95CXXX | CID Type Phone 8-Bit MCU |

| HT95L400-128QFP-A | LCD Type Phone 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT95C300 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C30P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C400 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C40P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:LCD Type Phone 8-Bit MCU |

| HT95CXXX | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。