- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82M99EE (Holtek Semiconductor Inc.) USB Mouse Encoder 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT82M99EE |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Mouse Encoder 8-Bit MCU |

| 中文描述: | USB鼠標(biāo)編碼器8位微控制器 |

| 文件頁數(shù): | 24/47頁 |

| 文件大小: | 336K |

| 代理商: | HT82M99EE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

HT82M99EE/HT82M99AE

Rev. 1.00

24

February 8, 2006

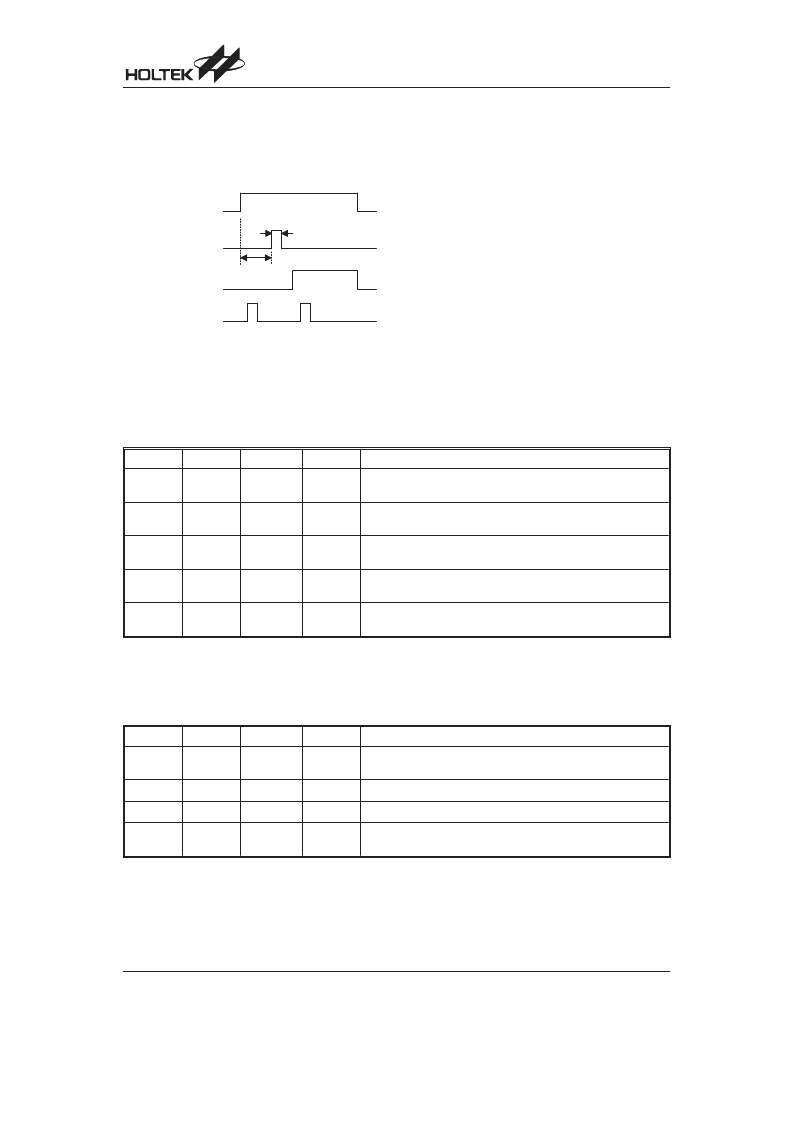

The device with remote wake-up function can wake-up

the USB Host by sending a wake-up pulse through

RMWK (bit 1 of USC). Once the USB Host receive the

wake-up signal from the HT8M99E, it will send a Re-

sume signal to the device. The timing is as follows:

To Configure the HT8M99E as PS2 Device

The HT8M99E can be defined as a USB interface or a

PS2 interface by configuring the SPS2 (bit 4 of the USR)

and SUSB (bit 5 of the USR). If SPS2=1, and SUSB=0,

the HT8M99E is defined as PS2 interface, pin USBD- is

now defined as PS2 Data pin and USBD+ is now de-

fined as PS2 Clk pin. The user can easily read or write to

the PS2 Data or PS2 Clk pin by accessing the corre-

sponding bit PS2DAI (bit 4 of the USC), PS2CKI (bit 5 of

the USC), PS2DAO (bit 6 of the USC) and S2CKO (bit 7

of the USC) respectively.

The user should make sure that in order to read the data

properly, the corresponding output bit must be set to 1 .

For example, if user wants to read the PS2 Data by

reading PS2DAI, the PS2DAO should be set to 1 . Oth-

erwise it always read a 0 .

If SPS2=0, and SUSB=1, the HT8M99E is defined as a

USB interface. Both the USBD- and USBD+ are driven

by the USB SIE of the HT8M99E. User only writes or

reads the USB data through the corresponding FIFO.

Both SPS2 and SUSB default is 0 .

- (

"

(

,

- B

+

/ / 8

"

/ ( (

- (

I/O Port Special Registers Definition

Port-A (12H)

PA

Bit No.

Label

Read/Write

Option

Functions

0

PA0

R/W

I/O (R/W) has pull-low and pull-high ROM code option.

Has falling edge wake-up ROM code option.

1

PA1

R/W

I/O (R/W) has pull-low and pull-high option.

Has falling edge wake-up option.

2~3

PA2~PA3

R/W

I/O (R/W) has pull-low and pull-high option.

Has falling edge and rising edge wake-up option.

4~6

PA4~PA6

R/W

I/O (R/W) has pull-high option.

Has falling edge wake-up option.

7

PA7

R/W

I/O (R/W) has pull-high option.

Has falling edge wake-up option, pin-shared with timer input pin.

PA (12H) Register

Port-A Control (13H)

This port configure the input or output mode of Port-A

PAC

Port-B Control (14H)

PB

Bit No.

Label

Read/Write

Option

Functions

0~1,

5~6

PB0~PB1,

PB5~PB6

Reserved bit.

2~3

PB2~PB3

R/W

I/O (R/W), has pull-low and pull-high option, ADC input.

4

PB4

R/W

I/O (R/W), has pull-high option, can wake-up, ADC input.

7

PB7

R/W

I/O (R/W), has pull-high option, ADC input, VRH input for ADC ex-

ternal mode, has wake-up capability.

PB (14H) Register

Port-B Control (15H)

This port configures the input or output mode of Port-B for I/O mode

PBC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82M99E | USB Mouse Encoder 8-Bit OTP MCU |

| HT82M99E-18 | USB Mouse Encoder 8-Bit OTP MCU |

| HT82M99E-20 | USB Mouse Encoder 8-Bit OTP MCU |

| HT82M9AAE | USB Mouse Encoder 8-Bit MCU with EEPROM |

| HT82M9AEE | USB Mouse Encoder 8-Bit MCU with EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82M99EE_08 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Mouse Encoder 8-Bit MCU |

| HT82M9AA | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Mouse Encoder 8-Bit MCU |

| HT82M9AAE | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Mouse Encoder 8-Bit MCU with EEPROM |

| HT82M9AE | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Mouse Encoder 8-Bit MCU |

| HT82M9AE_09 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Mouse Encoder 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。