- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82K68 (Holtek Semiconductor Inc.) Multimedia Keyboard Encoder OTP PDF資料下載

參數(shù)資料

| 型號(hào): | HT82K68 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | Multimedia Keyboard Encoder OTP |

| 中文描述: | 多媒體鍵盤編碼器檢察官辦公室 |

| 文件頁(yè)數(shù): | 9/40頁(yè) |

| 文件大?。?/td> | 260K |

| 代理商: | HT82K68 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

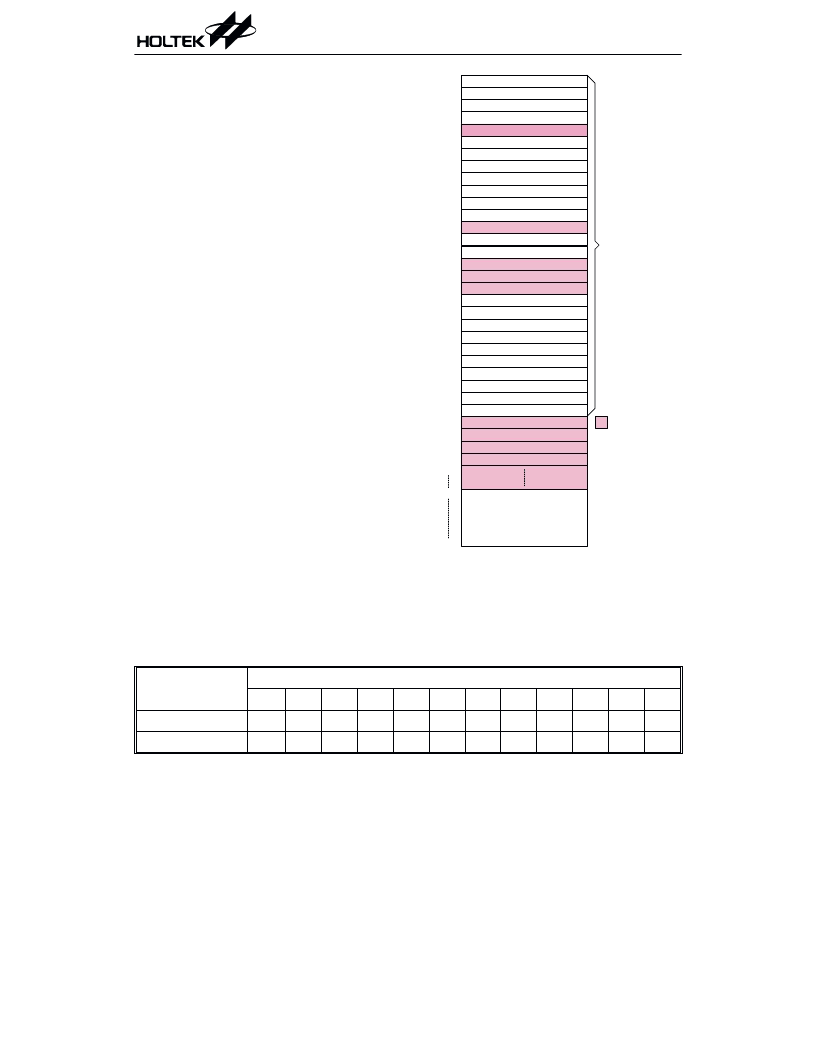

Instruction(s)

Table Location

11

10

9

8

7

6

5

4

3

2

1

0

TABRDC [m]

P11

P10

P9

P8

@7

@6

@5

@4

@3

@2

@1

@0

TABRDL [m]

1

0

1

1

@7

@6

@5

@4

@3

@2

@1

@0

HT82K68E

9

August 8, 2000

Preliminary

Note: *11~*0: Table location bits

@7~@0: Table location bits

P11~P8: Current program counter bits

Stack register

STACK

This is a special part of the memory which is

used to save the contents of the program coun-

ter(PC)only.Thestackisorganizedintosixlev-

els and is neither part of the data nor part of the

program space, and is neither readable nor

writeable. The activated level is indexed by the

stack pointer (SP) and is neither readable nor

writeable. At a subroutine call or interrupt ac-

knowledgement, the contents of the program

counter are pushed onto the stack. At the end of

a subroutine or an interrupt routine, signaled

by a return instruction (RET or RETI), the pro-

gram counter is restored to its previous value

from the stack. After a chip reset, the SP will

point to the top of the stack.

If the stack is full and a non-masked interrupt

takes place, the interrupt request flag will be re-

corded but the acknowledgement will be inhib-

ited. When the stack pointer is decremented (by

RETorRETI),theinterruptwillbeserviced.This

feature prevents stack overflow allowing the pro-

grammer to use the structure more easily. In a

similar case, if the stack is full and a CALL

subsequentlyexecuted,stackoverflowoccursand

the first entry will be lost (only the most recent

four return addresses are stored).

is

Data memory

RAM

The data memory is designed with 184

It is divided into two functional groups: special

function registers and general purpose data

memory (160 8). Most of them are read/write,

but some are read only.

8 bits.

The special function registers include the Indi-

rect Addressing register 0 (00H), the Memory

Pointer register 0 (MP0;01H), the Indirect Ad-

dressing register 1 (02H), the Memory Pointer

register 1 (MP1;03H), the Accumulator

(ACC;05H), the Program Counter Lower-byte

register (PCL;06H), the Table Pointer

(TBLP;07H), the Table Higher-order byte regis-

ter (TBLH;08H), the Watchdog Timer option Set-

ting register (WDTS;09H), the Status register

& !

& !

!

#

1 #

1 # =

-

!

!

!

1

1

. &

! ! & )

5 4 & 1 "6

. &

! ! & )

=

=

=

2 =

, =

3 =

4 =

( =

/ =

7 =

! =

1 =

=

=

=

8 =

=

=

=

2 =

, =

3 =

4 =

( =

/ =

7 =

! =

1 =

=

=

=

8 =

8 8 =

A & B

& &

=

4 =

RAM mapping

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82K94A | USB Multimedia Keyboard Encoder 8-Bit MCU |

| HT82K94E | USB Multimedia Keyboard Encoder 8-Bit MCU |

| HT82K94E_07 | USB Multimedia Keyboard Encoder 8-Bit MCU |

| HT82K95AE | USB Multimedia Keyboard Encoder 8-Bit MCU |

| HT82K95EE | USB Multimedia Keyboard Encoder 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82K68A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Multimedia Keyboard Encoder Body |

| HT82K68A_01 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit Multimedia Keyboard Encoder Mask MCU |

| HT82K68A-L | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Multimedia Keyboard Encoder 8-Bit MCU |

| HT82K68E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Multimedia Keyboard Encoder OTP |

| HT82K68E_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Multimedia Keyboard Encoder 8-Bit OTP MCU |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。