- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R62 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT46R62 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁數(shù): | 19/46頁 |

| 文件大小: | 401K |

| 代理商: | HT46R62 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

HT46R62/HT46C62

Rev. 1.60

19

July 14, 2005

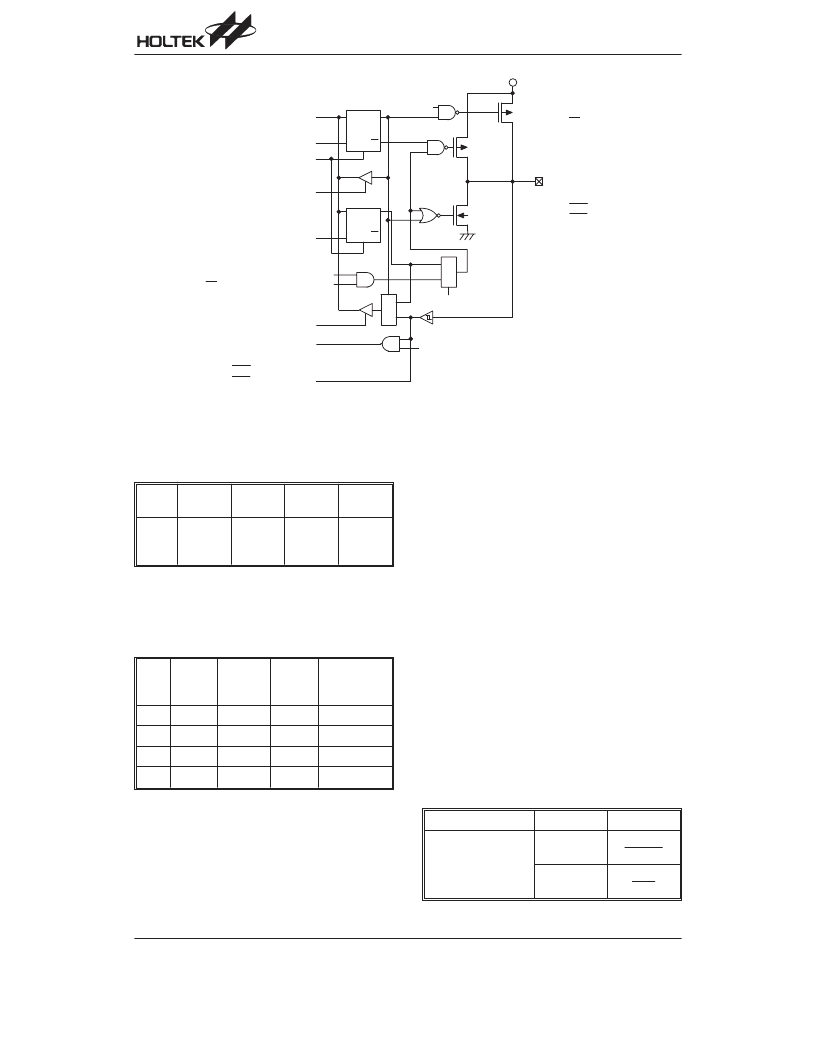

on PD0/PD1/PD2 (if PD0/PD1/PD2 is operating in out-

put mode). The I/O functions of PD0/PD1/PD2 are as

shown.

I/O

Mode

I/P

(Normal)

O/P

(Normal)

I/P

(PWM)

O/P

(PWM)

PD0

PD1

PD2

Logical

Input

Logical

Output

Logical

Input

PWM0

PWM1

PWM2

It is recommended that unused or not bonded out I/O

linesshouldbesetasoutputpinsbysoftwareinstruction

to avoid consuming power under input floating state.

The definitions of PFD control signal and PFD output

frequency are listed in the following table.

Timer

Timer

Preload

Value

PA3 Data

Register

PA3 Pad

State

PFD

Frequency

OFF

X

0

0

X

OFF

X

1

U

X

ON

N

0

0

X

ON

N

1

PFD

f

TMR

/[2 (M-N)]

Note:

X stands for unused

U stands for unknown

M is 256 for PFD

N is preload value for timer/event counter

f

TMR

is input clock frequency for timer/event

counter

PWM

The microcontroller provides 3 channels (6+2)/(7+1)

(dependent on options) bits PWM output shared with

PD0/PD1/PD2. The PWM channels have their data reg-

isters denoted as PWM0 (1AH), PWM1 (1BH) and

PWM2 (1CH). The frequency source of the PWM coun-

ter comes from f

SYS

. The PWM registers are three 8-bit

registers. The waveforms of PWM outputs are as

shown. Once the PD0/PD1/PD2 are selected as the

PWM outputs and the output function of PD0/PD1/PD2

are enabled (PDC.0/PDC.1/ PDC.2= 0 ), writing 1 to

PD0/PD1/PD2 data register will enable the PWM output

function and writing 0 will force the PD0/PD1/PD2 to

stay at 0 .

A(6+2) bits mode PWM cycle is divided into four modu-

lation cycles (modulation cycle 0~modulation cycle 3).

Each modulation cycle has 64 PWM input clock period.

In a (6+2) bit PWM function, the contents of the PWM

register is divided into two groups. Group 1 of the PWM

register is denoted by DC which is the value of

PWM.7~PWM.2. The group 2 is denoted by AC which is

the value of PWM.1~PWM.0.

In a (6+2) bits mode PWM cycle, the duty cycle of each

modulation cycle is shown in the table.

Parameter

AC (0~3)

Duty Cycle

Modulation cycle i

(i=0~3)

i<AC

DC+1

64

i AC

DC

64

!

" #

$

%

" #

&

'

" #

( #

)

" #

&

*

&

+

,

$ ,

,

,

$ ,

-

.

/ 0

(

.

/ 0

.

(

/

" 1

" " 2 + 2

1

/

" &

+

/ 2

&

&

* /

" &

+

&

+

1

, 1 3

$ , 1 3

-

,

! 4

5

1

,

4

1 % ,

%

,

$ ,

$

- ,

-

! ,

% ,

$

' ,

&

.

1 3 , 1 3 ,

,

,

$ ,

-

Input/Output Ports

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46C63 | A/D with LCD Type 8-Bit MCU |

| HT46C63-100QEP-A | A/D with LCD Type 8-Bit MCU |

| HT46C63-56SSOP-A | A/D with LCD Type 8-Bit MCU |

| HT46R63 | A/D with LCD Type 8-Bit MCU |

| HT46C64 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R63 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64_06 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。