- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R62 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT46R62 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁數(shù): | 17/46頁 |

| 文件大小: | 401K |

| 代理商: | HT46R62 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

HT46R62/HT46C62

Rev. 1.60

17

July 14, 2005

flows,thecounterisreloadedfromthetimer/eventcoun-

ter register and issues an interrupt request, as in the

other two modes, i.e., event and timer modes.

To enable the counting operation, the Timer ON bit

(TON; bit 4 of TMRC) should be set to 1. In the pulse

width measurement mode, the TON is automatically

cleared after the measurement cycle is completed. But

in the other two modes, the TON can only be reset by in-

structions. The overflow of the Timer/Event Counter is

one of the wake-up sources and can also be applied to a

PFD (Programmable Frequency Divider) output at PA3

by options. Only one PFD can be applied to PA3 by op-

tions . No matter what the operation mode is, writing a 0

to ETI disables the related interrupt service. When the

PFD function is selected, executing SET [PA].3 in-

struction to enable PFD output and executing

CLR

[PA].3 instruction to disable PFD output.

In the case of timer/event counter OFF condition, writing

data to the timer/event counter preload register also re-

loads that data to the timer/event counter. But if the

timer/event counter is turn on, data written to the

timer/event counter is kept only in the timer/event coun-

ter preload register. The timer/event counter still contin-

ues its operation until an overflow occurs.

When the timer/event counter (reading TMR) is read,

the clock is blocked to avoid errors, as this may results

2

8

& 2 A (

(

-

0

"

(

(

$

+

+

2

( '

%

(

2

/ 7 @

(

-

8

(

2

(

/ 7 @

(

-

8

(

:

;

( *

/ 7

(

2

/ 7 (

!

&

1

&

,

+

: 3 =

; (

( : 6 =

;

'

(

+ -

-

(

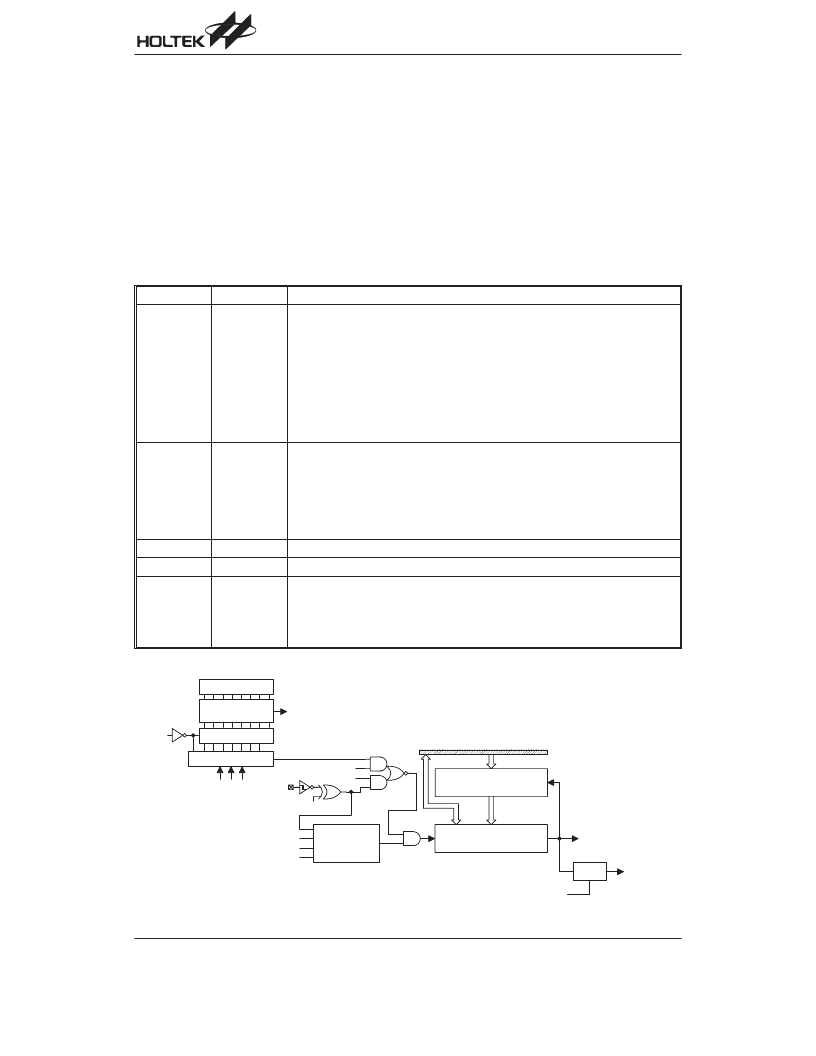

Timer/Event Counter

Bit No.

Label

Function

0

1

2

PSC0

PSC1

PSC2

To define the prescaler stages.

PSC2, PSC1, PSC0=

000: f

INT

=f

SYS

001: f

INT

=f

SYS

/2

010: f

INT

=f

SYS

/4

011: f

INT

=f

SYS

/8

100: f

INT

=f

SYS

/16

101: f

INT

=f

SYS

/32

110: f

INT

=f

SYS

/64

111: f

INT

=f

SYS

/128

3

TE

Defines the TMR active edge of the timer/event counter:

In Event Counter Mode (TM1,TM0)=(0,1):

1:count on falling edge;

0:count on rising edge

In Pulse Width measurement mode (TM1,TM0)=(1,1):

1: start counting on the rising edge, stop on the falling edge;

0: start counting on the falling edge, stop on the rising edge

4

TON

Enable/disable timer counting (0=disabled; 1=enabled)

5

Unused bit, read as 0

6

7

TM0

TM1

Defines the operating mode (TM1, TM0)

01= Event count mode (External clock)

10= Timer mode (Internal clock)

11= Pulse Width measurement mode (External clock)

00= Unused

TMRC (0EH) Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46C63 | A/D with LCD Type 8-Bit MCU |

| HT46C63-100QEP-A | A/D with LCD Type 8-Bit MCU |

| HT46C63-56SSOP-A | A/D with LCD Type 8-Bit MCU |

| HT46R63 | A/D with LCD Type 8-Bit MCU |

| HT46C64 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R63 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64_06 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R64_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46R65 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。