- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R46 (Holtek Semiconductor Inc.) Cost-Effective A/D Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT46R46 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | Cost-Effective A/D Type 8-Bit MCU |

| 中文描述: | 成本效益的A / D型8位微控制器 |

| 文件頁數(shù): | 18/42頁 |

| 文件大?。?/td> | 291K |

| 代理商: | HT46R46 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

HT46R46/HT46C46/HT46R47/HT46C47

Rev. 1.00

18

December 28, 2004

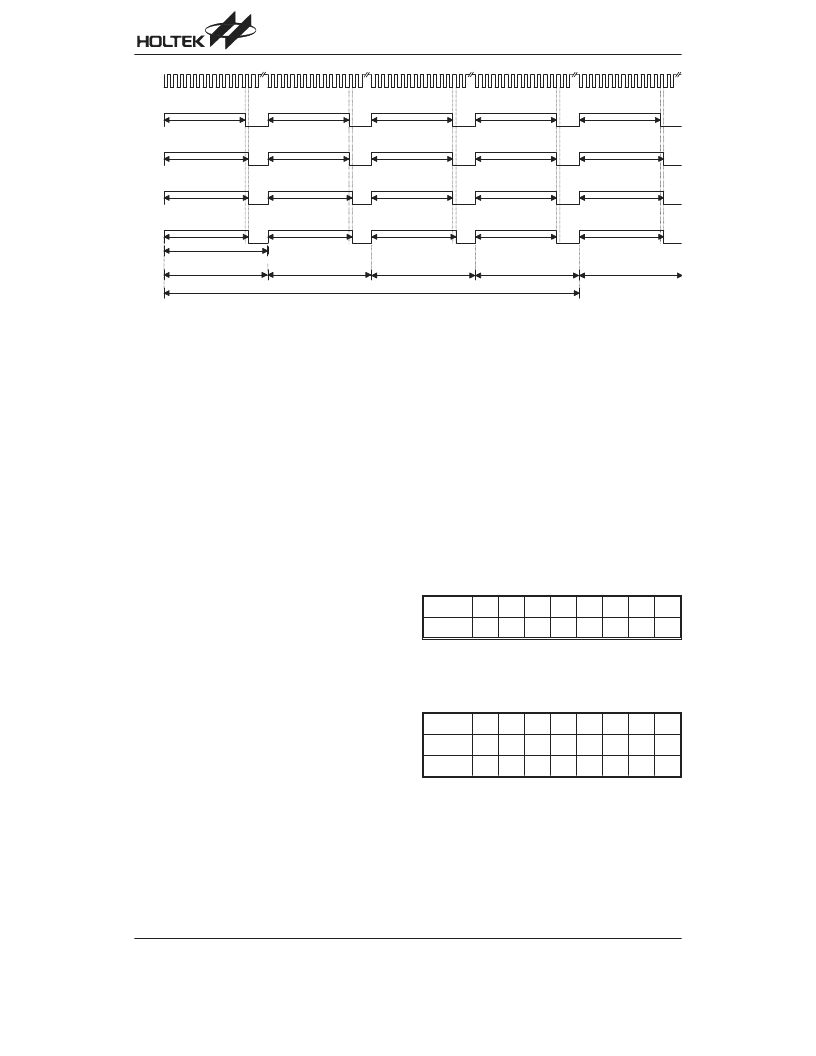

A/D Converter

The 4 channels and 8-bit resolution for the HT46R46/

HT46C46 or 9-bit resolution for the HT46R47/HT46C47

A/D converter are implemented in this microcontroller.

The reference voltage is VDD. The A/D converter con-

tains 3 special registers for the HT46R46/HT46C46

which are; ADR (21H), ADCR (22H) and ACSR (23H) or

contains 4 special registers for the HT46R47/HT46C47

whice are; ADRL (20H), ADRH (21H), ADCR (22H) and

ACSR (23H). The ADR is HT46R46/ HT46C46 an A/D

result register that is read-only. The ADRH and ADRL

are HT46R47/HT46C47 A/D result register higher-order

byte and lower-order byte which are read-only. After the

A/D conversion is completed, the ADR (HT46R46/

HT46C46) or ADRL, ADRH (HT46R47/HT46C47)

should be read to get the conversion result data. The

ADCR is an A/D converter control register, which de-

fines the A/D channel number, analog channel select,

start A/D conversion control bit and the end of A/D con-

version flag. If the users want to start an A/D conversion,

define PB configuration, select the converted analog

channel, and give START bit a raising edge and a falling

edge (0

EOCB bit is cleared and an A/D converter interrupt oc-

curs (if the A/D converter interrupt is enabled). The

ACSR is A/D clock setting register, which is used to se-

lect the A/D clock source.

1

0). At the end of A/D conversion, the

The A/D converter control register is used to control the

A/D converter. The bit2~bit0 of the ADCR are used to

select an analog input channel. There are a total of four

channels to select. The bit5~bit3 of the ADCR are used

to set PB configurations. PB can be an analog input or

as digital I/O line decided by these 3 bits. Once a PB line

is selected as an analog input, the I/O functions and

pull-high resistor of this I/O line are disabled, and the

A/D converter circuit is power on. The EOCB bit (bit6 of

the ADCR) is end of A/D conversion flag. Check this bit

to know when A/D conversion is completed. The START

bit of the ADCR is used to begin the conversion of A/D

converter. Give START bit a raising edge and falling

edge that means the A/D conversion has started. In or-

der to ensure the A/D conversion is completed, the

START should stay at 0 until the EOCB is cleared to

0 (end of A/D conversion).

The bit 7 of the ACSR is used for testing purpose only. It

can not be used for the users. The bit1 and bit0 of the

ACSR are used to select A/D clock sources.

When the A/D conversion is completed, the A/D inter-

rupt request flag is set. The EOCB bit is set to 1 when

the START bit is set from 0 to 1 .

Register Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

ADR

D7

D6

D5

D4

D3

D2

D1

D0

Note:

D0~D7 is A/D conversion result data bit

LSB~MSB.

ADR (21H) Register for HT46R46/HT46C46

Register Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

ADRL

D0

ADRH

D8

D7

D6

D5

D4

D3

D2

D1

Note:

D0~D8 is A/D conversion result data bit

LSB~MSB.

ADRL(20H),ADRH(21H)RegisterforHT46R47/HT46C47

)

/

+

G

+

H I

1 1

G

+

H I

1

+

G

+

H I

1

+

G

+

H I

1 ,

+

+

" $ " 0

B

5 )

/

5

5 5

5 5

5 5

5

5

5

5

5

5

5

5 5

5 5

5

5

5 5

5

5 5

5 5

5 5

&

0

!

" $ " 0

1

+

&

0

!

! & B 5

)

/

&

0

!

" $ " 0

&

0

!

" $ " 0

&

0

!

" $ " 0

,

&

0

!

" $ " 0

1

PWM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46C62 | A/D with LCD Type 8-Bit MCU |

| HT46R62 | A/D with LCD Type 8-Bit MCU |

| HT46C63 | A/D with LCD Type 8-Bit MCU |

| HT46C63-100QEP-A | A/D with LCD Type 8-Bit MCU |

| HT46C63-56SSOP-A | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R46_08 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46R46E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46R46E_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46R46-H | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit OTP MCU |

| HT46R47 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit OTP Battery Charger Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。