- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385398 > HT36A0 (Holtek Semiconductor Inc.) 8-Bit Music Synthesizer MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT36A0 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit Music Synthesizer MCU |

| 中文描述: | 8位微控制器音樂合成器 |

| 文件頁(yè)數(shù): | 15/23頁(yè) |

| 文件大?。?/td> | 257K |

| 代理商: | HT36A0 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

HT36A0

Rev. 1.20

15

June 18, 2003

In pulse width measurement mode with the TON and TE

bitsequaltoone,oncetheTMRhasreceivedatransient

from low to high (or high to low; if the TE bit is 0) it will

start counting until the TMR returns to the original level

and resets the TON. The measured result will remain in

the even if the activated transient occurs again. In other

words, only one cycle measurements can be done. Until

setting the TON, the cycle measurement will function

again as long as it receives further transient pulse. Note

that, in this operating mode, the timer/event counter

starts counting not according to the logic level but ac-

cording to the transient edges. In the case of counter

overflows, the counter is reloaded from the timer/event

counterpreloadregisterandissuestheinterruptrequest

just like the other two modes.

To enable the counting operation, the Timer ON bit

(TON; bit 4 of TMR0C/TMR1C) should be set to 1. In the

pulse width measurement mode, the TON will be

cleared automatically after the measurement cycle is

completed.ButintheothertwomodestheTONcanonly

be reset by instruction. The overflow of the timer/event

counter is one of the wake-up sources. No matter what

the operation mode is, writing a 0 to ET0I/ET1I can dis-

able the corresponding interrupt service.

In the case of timer/event counter OFF condition, writing

data to the Timer/event Counter Preload register will

also reload that data to the timer/event counter. But if

the timer/event counter is turned on, data written to the

timer/event counter will only be kept in the timer/event

counter preload register. The timer/event counter will

still operate until overflow occurs.

When

TMR0H/TMR1H) is read, the clock will be blocked to

avoid errors. As this may results in a counting error,

this must be taken into consideration by the program-

mer.

the

timer/event

counter

(reading

The two timer counters of HT36A0 are internal clock

mode only, so only Timer mode can be selected. There-

fore the (TM1, TM0) bits can only be set to (TM1,TM0) =

(1,0), and the other clock modes are invalid.

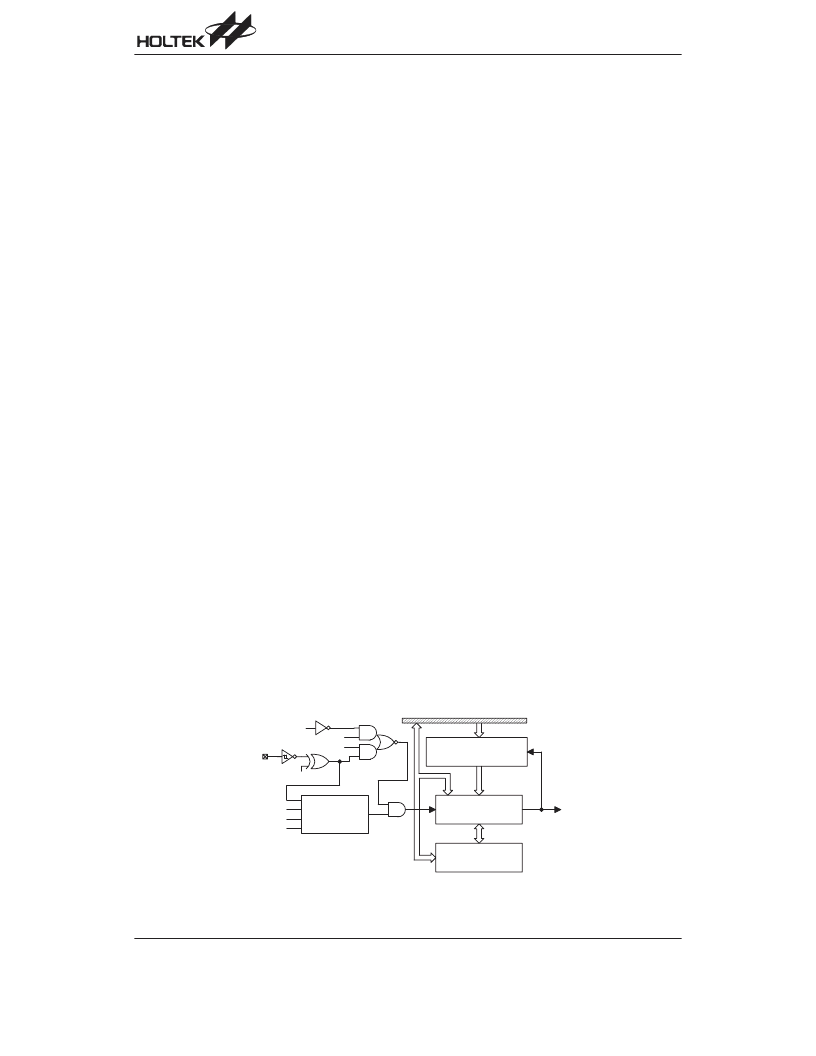

Input/Output Ports

There are 28 bidirectional input/output lines labeled

from PAto PD, which are mapped to the data memory of

[12H], [14H], [16H], [18H] respectively. All these I/O

ports can be used for input and output operations. For

input operation, these ports are non-latching, that is, the

inputs must be ready at the T2 rising edge of instruction

MOV A,[m] (m=12H, 14H, 16H or 18H). For output oper-

ation, all data is latched and remains unchanged until

the output latch is rewritten.

Each I/O line has its own control register (PAC, PBC,

PCC, PDC) to control the input/output configuration.

With this control register, CMOS output or Schmitt Trig-

ger input with or without pull-high resistor (mask option)

structures can be reconfigured dynamically under soft-

ware control. To function as an input, the corresponding

latch of the control register must write a

pull-high resistance will exhibit automatically if the

pull-high option is selected. The input source also de-

pends on the control register. If the control register bit is

1 . The

1 , input will read the pad state. If the control register bit

is 0 , the contents of the latches will move to the internal

bus. The latter is possible in read-modify-write instruc-

tion. For output function, CMOS is the only configura-

tion. These control registers are mapped to locations

13H, 15H, 17H and 19H).

Afterachipreset,theseinput/outputlinesremainathigh

levels or floating (mask option). Each bit of these in-

put/output latches can be set or cleared by the SET [m].i

or CLR [m].i (m=12H, 14H, 16H or 18H) instruction.

Some instructions first input data and then follow the

output operations. For example, the SET [m].i, CLR

[m].i, CPL [m] and CPLA[m] instructions read the entire

port states into the CPU, execute the defined operations

(bit-operation), and then write the results back to the

latches or the accumulator.

Each line of port A has the capability to wake-up the de-

vice.

" 7

= .

3 6 :

'

'

' #

'

'

'

+

. E

A

=

3 A

.

3

3

' =

>

.

3

.

3

A .

4

' =

>

3

.

.

3

A

>

0 3 @

' 3 . 1

& 3 @ .

7

0 0

+

Timer/Event Counter 0/1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT36A1 | Music Synthesizer 8-Bit MCU |

| HT36A2 | 8-Bit Music Synthesizer MCU |

| HT36A3 | 8-Bit Music Synthesizer MCU |

| HT36A4 | 8-Bit Music Synthesizer MCU |

| HT3810 | 128 NOTE MELODY GENERATORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT36A0(48DIP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| HT36A1 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Music Synthesizer 8-Bit MCU |

| HT36A2 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit Music Synthesizer MCU |

| HT36A3 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit Music Synthesizer MCU |

| HT36A4 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Music Synthesizer 8-Bit MCU |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。