- 您現在的位置:買賣IC網 > PDF目錄371881 > HPC PDF資料下載

參數資料

| 型號: | HPC |

| 文件頁數: | 2/30頁 |

| 文件大小: | 361K |

| 代理商: | HPC |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

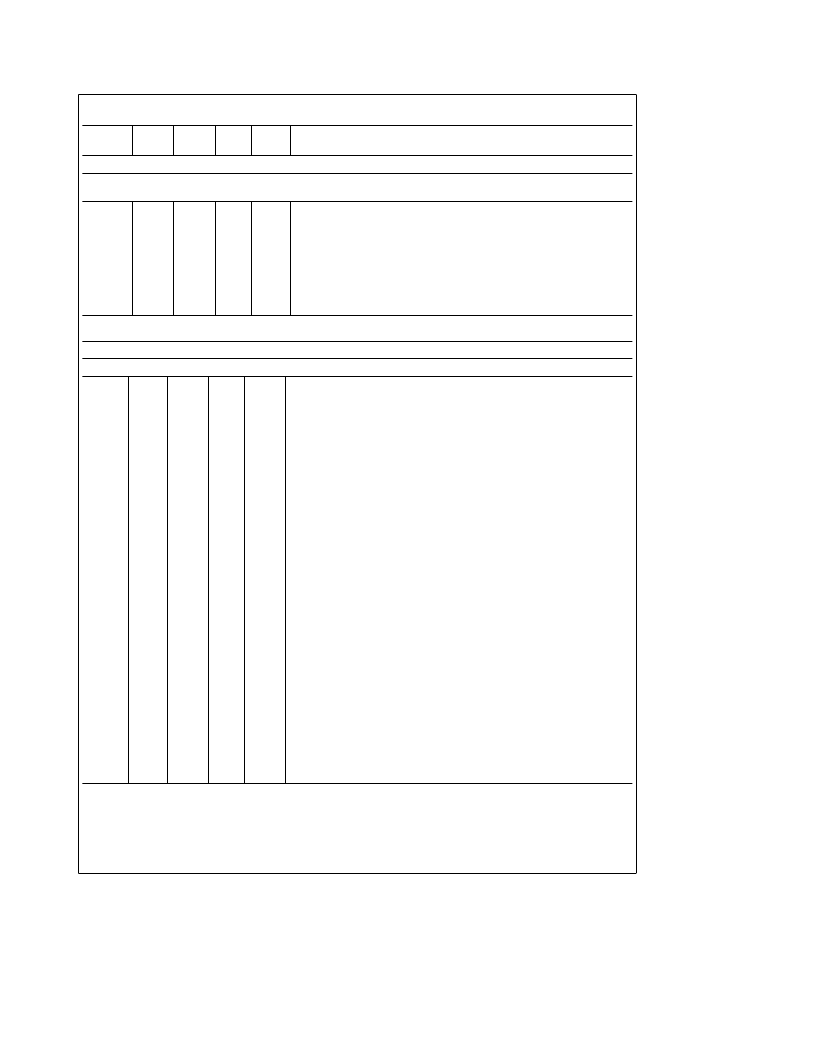

Signal Descriptions

Signal

Reset

Active

Type

Load

Factor

Description

PORT A

Port A is a 16-bit bidirectional I/O port with a data direction register to enable each separate pin to be individually defined as an input

or output. When accessing external memory, Port A may be used as the multiplexed address/data bus.

PA(0:15)

*

Z

B

Port ADthis may be configured as a 16-bit Addr/Data bus or a 16-bit general

purpose I/O port.

Port A data in.

Port A data out.

Port A bidirectional control.

Defines the configuration of Port A. 1

e

Address/Data bus, 0

e

General

purpose I/O port.

Read Port A onto the internal data bus. All memory locations connected to Port

A should be decoded and input on this pin when in Addr/Data bus mode.

PI(0:15)

PD(0:15)

PE(0:15)

EXAC

I

2

U

1

O

O

I

1

RDEX

H

I

1

*

PA is created when PI, PD and PE are connected to a 4 mA I/O buffer macro. Allowable macros include BF0B4D, BF0B4N, BF0B4U, BB0B4D, BB0B4N, and

BB0B4U.

PORT I

Port I is an 8-bit input port that can be read as general purpose inputs or can be used for the following functions:

I0

I1

I

I

1

1

General purpose input.

Port I: bit 1 of Port I.

Interrupt: rising edge triggered non-maskable interrupt (NMI).

IRPD: bit 1 is set when interrupt is pending and is reset when interrupt is

acknowledged.

Halt & Idle mode: rising edge will exit Halt or Idle mode.

Entering Halt with NMI high: stop oscillator, stop C1 & C2 at C1

e

0 C2

e

1.

Entering Halt with NMI low: logic is stopped, but oscillator is kept alive.

Port I: bit 2 of Port I.

Interrupt: Enabled if bit 2 of ENIR is set. Rising/falling edge trigger is selected if

bit 2 of IRCD is set/reset.

IRPD: bit 2 is set when interrupt is pending and is reset when interrupt is

acknowledged.

Capture trigger input: Value of Timer T0 is copied into I2CR register when

interrupt occurs.

Port I: bit 3 of Port I.

Interrupt: Enabled if bit 3 of ENIR is set. Rising/falling edge trigger is selected if

bit 3 of IRCD is set/reset.

IRPD: bit 3 is set when interrupt is pending and is reset when interrupt is

acknowledged.

Capture trigger input: Value of Timer T0 is copied into I3CR register when

interrupt occurs.

PORT I: bit 4 of Port I.

Interrupt: Enabled if bit 4 of ENIR is set. Rising/falling edge trigger is selected if

bit 4 of IRCD is set/reset.

IRPD: bit 4 is set when interrupt is pending and is reset when interrupt is

acknowledged.

Capture trigger input: Value of Timer T0 is copied into I4CR register when

interrupt occurs.

Port I: Bit 5 of Port I.

UWIRE: Serial input to SIO shift register, bit 0 (MWIN).

General purpose input.

General purpose input.

I2

I

1

I3

I

1

I4

I

1

I5

I6

I7

I

I

I

1

1

1

Z

e

Tristate

H

e

Active High

U

e

Unknown

L

e

Active Low

I

e

Input

B

e

Bidirectional

O

e

Output

2

相關PDF資料 |

PDF描述 |

|---|---|

| HPE2411C | Peripheral Miscellaneous |

| HPF240D20 | |

| HPF240D30 | |

| HPF240D30R | |

| HPF240D30RS | |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HPC-001 | 制造商:PREMO 制造商全稱:PREMO CORPORATION S.L 功能描述:High power planar chokes for HV applications |

| HPC-002 | 制造商:PREMO 制造商全稱:PREMO CORPORATION S.L 功能描述:High power planar chokes for HV applications |

| HPC0201A0R7BXZT1 | 功能描述:硅電容器 10V 0.7pF .1pF Tol RoHS:否 制造商:IPDiA 電容:1 uF 容差:15 % 電壓額定值:5 V 溫度系數:0.5 % 工作溫度范圍:- 55 C to + 150 C 封裝 / 箱體:1206 外殼高度:0.4 mm 系列:HSSC427.xxx 類型:1206 High Stability Silicon Capacitor |

| HPC0201AKIT01 | 功能描述:電容套件 SILICON RF CAP KIT 0.4-39pF RoHS:否 制造商:Nichicon 電容范圍:10 uF to 680 uF 公差范圍: 電壓范圍:6.3 V to 25 V 產品:Aluminum Organic Polymer Capacitor Kit |

| HPC02WE1050 | 制造商:TE Connectivity 功能描述:Labels Dot Matrix Printable Label Fabric White 50.8x5.1mm |

發(fā)布緊急采購,3分鐘左右您將得到回復。