- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385388 > HMS87C1304A (Hynix Semiconductor Inc.) CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | HMS87C1304A |

| 廠商: | Hynix Semiconductor Inc. |

| 英文描述: | CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER |

| 中文描述: | CMOS單芯片8位微控制器 |

| 文件頁數(shù): | 22/70頁 |

| 文件大?。?/td> | 977K |

| 代理商: | HMS87C1304A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

HMS87C1304A/HMS87C1302A

HYUNDAI MicroElectronics

22

Preliminary

Jan. 2001

8.3 Data Memory

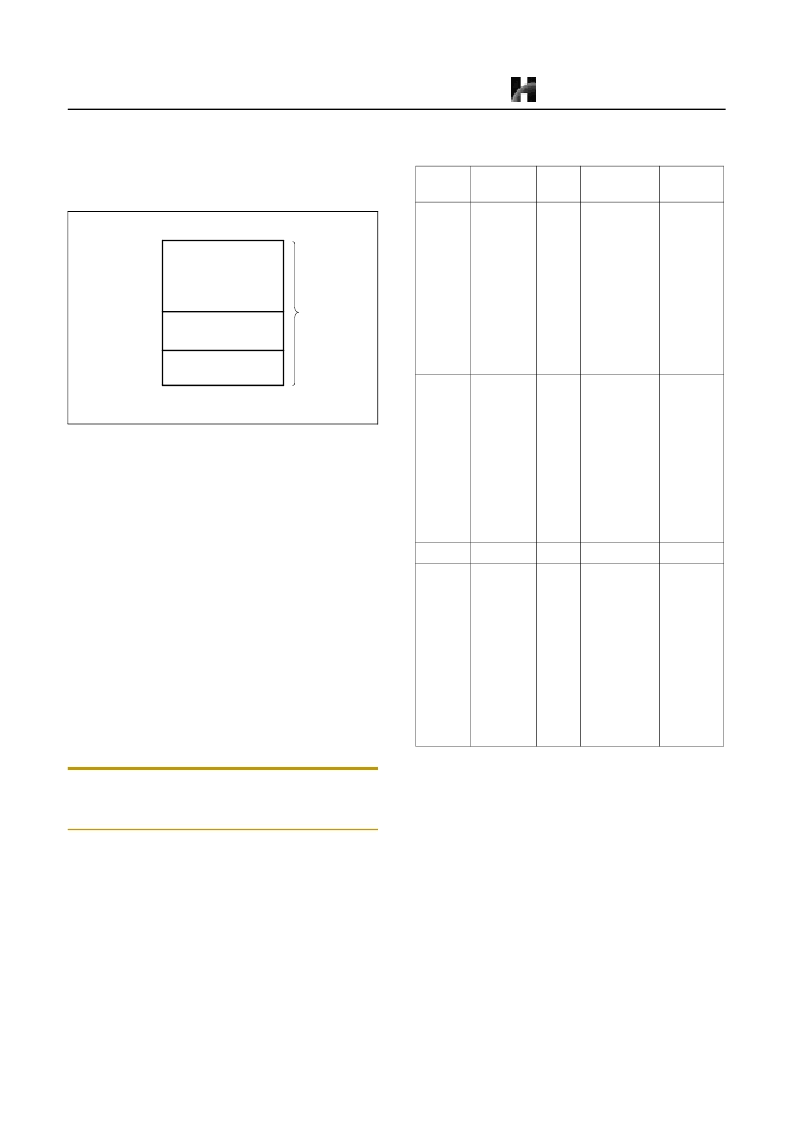

Figure 8-7 shows the internal Data Memory space availa-

ble. Data Memory is divided into two groups, a user RAM

(including Stack) and control registers.

Figure 8-7 Data Memory Map

User Memory

The HMS87C1304A and HMS87C1302A has 128

×

8 bits

for the user memory (RAM).

Control Registers

The control registers are used by the CPU and Peripheral

function blocks for controlling the desired operation of the

device. Therefore these registers contain control and status

bits for the interrupt system, the timer/ counters, analog to

digital converters and I/O ports. The control registers are in

address range of 0C0

H

to 0FF

H

.

Note that unoccupied addresses may not be implemented

on the chip. Read accesses to these addresses will in gen-

eral return random data, and write accesses will have an in-

determinate effect.

More detailed informations of each register are explained

in each peripheral section.

Note:

Write only registers can not be accessed by bit ma-

nipulation instruction. Do not use read-modify-write

instruction. Use byte manipulation instruction.

Example; To write at CKCTLR

LDM

CKCTLR,#09H ;Divide ratio

÷

16

USER

MEMORY

(including STACK)

CONTROL

REGISTERS

0000H

00BFH

00C0H

00FFH

PAGE0

007FH

0080H

Address

Symbol

R/W

RESET

Value

Addressing

mode

0C0H

0C1H

0C2H

0C3H

0C4H

0C5H

0C6H

0C7H

0CAH

0CBH

0CCH

RA

RAIO

RB

RBIO

RC

RCIO

RD

RDIO

RAFUNC

RBFUNC

PUPSEL

R/W

W

R/W

W

R/W

W

R/W

W

W

W

W

Undefined

0000_0000

Undefined

0000_0000

Undefined

----_--00

Undefined

----_0000

0000_0000

0000_0000

----_--00

byte, bit

1

byte

2

byte, bit

byte

byte, bit

byte

byte, bit

byte

byte

byte

byte

0D0H

0D1H

0D1H

0D1H

0D2H

0D3H

0D3H

0D4H

0D4H

0D4H

0D5H

TM0

T0

TDR0

CDR0

TM1

TDR1

T1PPR

T1

CDR1

T1PDR

PWM0HR

R/W

R

W

R/W

W

W

R

R

R/W

W

--00_0000

0000_0000

1111_1111

0000_0000

0000_0000

1111_1111

1111_1111

0000_0000

0000_0000

0000_0000

----_0000

byte, bit

byte

byte

byte

byte, bit

byte

byte

byte

byte

byte, bit

byte

0DEH

BUR

W

1111_1111

byte

0E2H

0E3H

0E4H

0E5H

0E6H

0EAH

0EBH

0ECH

0ECH

0EDH

0EDH

0EFH

IENH

IENL

IRQH

IRQL

IEDS

ADCM

ADCR

BITR

CKCTLR

WDTR

WDTR

PFDR

R/W

R/W

R/W

R/W

R/W

R/W

R

R

W

R

W

R/W

0000_----

000-_----

0000_----

000-_----

----_0000

--00_0001

Undefined

0000_0000

-001_0111

0000_0000

0111_1111

----_-100

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte

byte

byte

byte

byte

byte, bit

Table 8-1 Control Registers

1. “byte, bit” means that register can be addressed by not only bit

but byte manipulation instruction.

2. “byte” means that register can be addressed by only byte

manipulation instruction. On the other hand, do not use any

read-modify-write instruction such as bit manipulation for

clearing bit.

Preimnary

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMS87C1302AD | CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER |

| HMS87C1304AD | CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER |

| HMS99C51 | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS99C52 | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS9XC7132 | DATA SHEET REV.2.0(PRELIMINARY) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMS87C1304AD | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER |

| HMS87C1404B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS87C1404BD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS87C1404BSK | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS87C1408B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。