- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385388 > HMP8190EVAL1 (Intersil Corporation) NTSC/PAL Video Encoder PDF資料下載

參數(shù)資料

| 型號: | HMP8190EVAL1 |

| 廠商: | Intersil Corporation |

| 英文描述: | NTSC/PAL Video Encoder |

| 中文描述: | NTSC / PAL視頻編碼器 |

| 文件頁數(shù): | 5/32頁 |

| 文件大小: | 227K |

| 代理商: | HMP8190EVAL1 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

5

Video Timing Control

The pixel input data and the output video timing of the

HMP8190/HMP8191 are at 50 or 59.94 fields per second

interlaced. The timing is controlled by the BLANK, HSYNC,

VSYNC, FIELD, and CLK2 pins.

HSYNC, VSYNC, and Field Timing

The leading edge of HSYNC indicates the beginning of a

horizontal sync interval. If HSYNC is an output, it is asserted

for about 4.7

μ

s. If HSYNC is an input, it must be active for at

least two CLK2 periods. The width of the analog horizontal

sync tip is determined from the video standard and does not

depend on the width of HSYNC.

The leading edge of VSYNC indicates the beginning of a

vertical sync interval. If VSYNC is an output, it is asserted for

3 scan lines in (MM) NTSC and (M, N) PAL modes or 2.5

scan lines in (B, D, G, H, I, NC) PAL modes. If VSYNC is an

input, it must be asserted for at least two CLK2 periods.

When HSYNC and VSYNC are configured as outputs, their

leading edges will occur simultaneously at the start of an

odd field. At the start of an even field, the leading edge of

VSYNC occurs in the middle of the line.

When HSYNC and VSYNC are configured as inputs, the

HMP8190/HMP8191 provides a programmable HSYNC

window for determining FIELD. The window is specified with

respect to the leading or trailing edge of VSYNC. The edge

is selected in the field control register. When HSYNC is

found inside the window, then the encoder sets FIELD to the

value specified in the field control register.

The HMP8190/HMP8191 provides programmable timing for

the VSYNC input. At the active edge of VSYNC, the encoder

resets its vertical half-line counter to the value specified by

the field control register. This allows the input and output

syncs to be offset, although the data must still be aligned.

The FIELD signal is always an output and changes state

near each leading edge of VSYNC. The delay between the

syncs and FIELD depends on the encoder’s operating mode

as summarized in Table 4. In modes in which the encoder

uses CLK to gate its inputs and outputs, the FIELD signal

may be delayed 0-12 additional CLK2 periods.

Figure 4 illustrates the HSYNC, VSYNC, and FIELD general

timing for (M) NTSC and (M, N) PAL. Figure 5 illustrates the

general timing for (B, D, G, H, I, NC) PAL. In the figures, all

the signals are shown active low (their reset state), and

FIELD is low during odd fields.

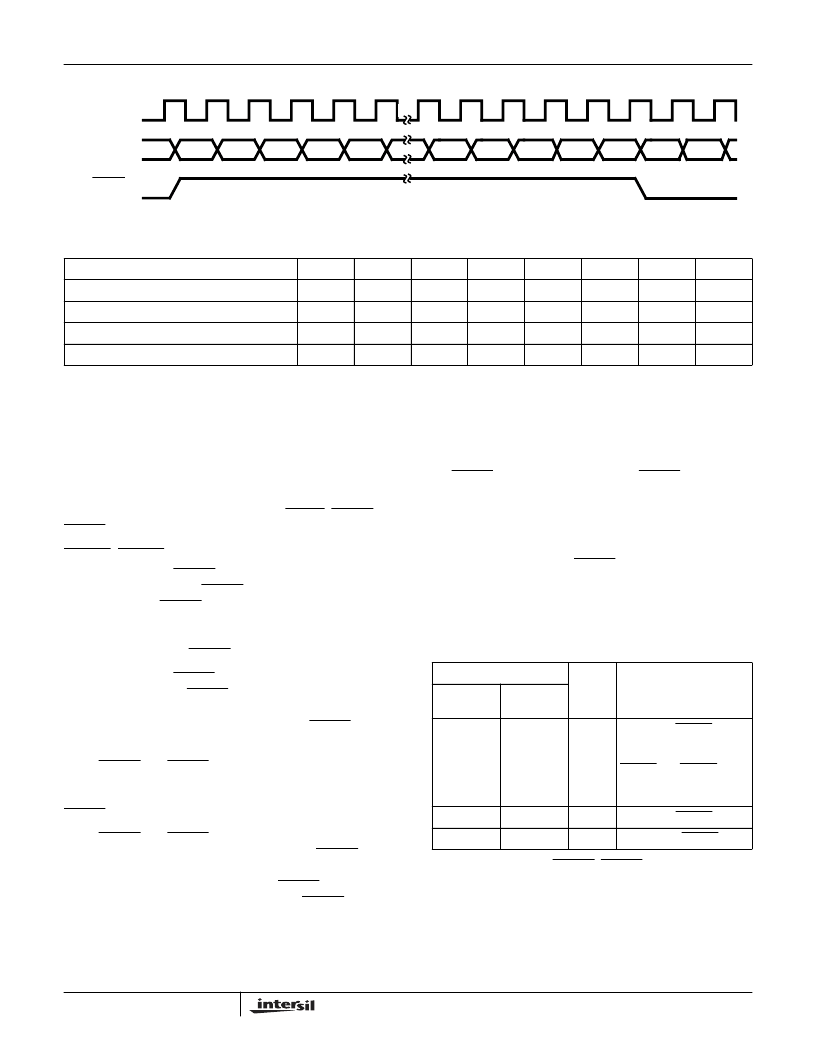

FIGURE 3. PIXEL INPUT TIMING - BT.656

TABLE 3. BT.656 EAV AND SAV SEQUENCES

PIXEL INPUT

P15

P14

P13

P12

P11

P10

P9

P8

Preamble Word 1

1

1

1

1

1

1

1

1

Preamble Word 2

0

0

0

0

0

0

0

0

Preamble Word 3

0

0

0

0

0

0

0

0

Status Word

1

F

V

H

P3

P2

P1

P0

NOTE:

F: 0 = Field 1; 1 = Field 2

V: 0 = Active Line; 1 = Vertical Blanking

H: 0 = Start Active Video; 1 = End Active Video

P3 - P0: Protection bits; Ignored

Cb 2

Y 2

Cr 2

Y 3

Cb 4

Y 4

CLK2

P8-P15

“FF”

"00"

BLANK

(OUTPUT)

“00”

EAV

“10”

“10”

“80”

TABLE 4. FIELD OUTPUT TIMING

OPERATING MODE

CLK2

DELAY

COMMENTS

SYNC I/O

DIRECTION

BLANK I/O

DIRECTION

Input

Input

148

FIELD lags VSYNC switch-

ing from odd to even.

FIELD lags the earlier of

VSYNC and HSYNC when

syncs are aligned when

switching from even to odd.

Input

Output

138

FIELD lags VSYNC.

Output

Don’t Care

32

FIELD leads VSYNC.

HMP8190, HMP8191

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMP8191 | NTSC/PAL Video Encoder |

| HMP8191CN | NTSC/PAL Video Encoder |

| HMPS650 | NPN SILICON TRANSISTOR |

| HMPSH10 | NPN EPITAXIAL PLANAR TRANSISTOR |

| HMS77C1000A | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMP8191 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8191CN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8201CN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Compression/Expansion Circuit |

| HMP820SGR32GM | 制造商:Advanced Micro Devices 功能描述:PHENOM II MOBILE X3 P820 25W S1G4 - Trays |

| HMP9701 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:AC’97 Audio Codec |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。