- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371861 > HMP8115 (Intersil Corporation) NTSC/PAL Video Decoder PDF資料下載

參數(shù)資料

| 型號: | HMP8115 |

| 廠商: | Intersil Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL視頻解碼器 |

| 文件頁數(shù): | 32/43頁 |

| 文件大小: | 183K |

| 代理商: | HMP8115 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

32

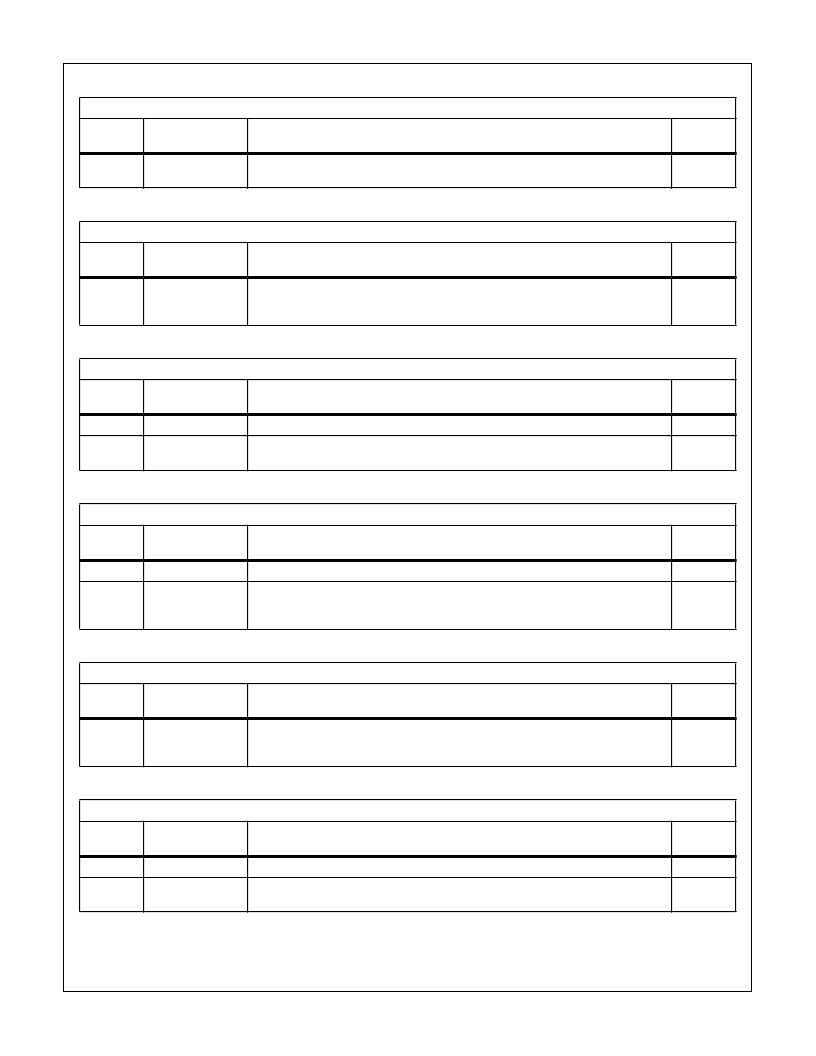

TABLE 34. CLOSED CAPTION_EVEN_B DATA REGISTER

SUB ADDRESS = 23

H

BIT

NO.

FUNCTION

DESCRIPTION

RESET

STATE

15-8

Even Field

Caption Data

If even field captioning is enabled and present, this register is loaded with the second

eight bits of caption data on line 281, 284, or 335. Data written to this register is ignored.

80

H

TABLE 35. WSS_ODD_A DATA REGISTER

SUB ADDRESS = 24

H

BIT

NO.

FUNCTION

DESCRIPTION

RESET

STATE

7-0

Odd Field

WSS Data

If odd field WSS is enabled and present, this register is loaded with the first eight bits of

WSS information on line 17, 20, or 23. Bit 0 corresponds to the first bit of WSS informa-

tion. Data written to this register is ignored.

00

H

TABLE 36. WSS_ODD_B DATA REGISTER

SUB ADDRESS = 25

H

BIT

NO.

FUNCTION

DESCRIPTION

RESET

STATE

15-14

Reserved

00

B

13-8

Odd Field

WSS Data

If odd field WSS is enabled and present, this register is loaded with the second six bits of

WSS information on line 17, 20, or 23. Data written to this register is ignored.

000000

B

TABLE 37. WSS_CRC_ODD DATA REGISTER

SUB ADDRESS = 26

H

BIT

NO.

FUNCTION

DESCRIPTION

RESET

STATE

7-6

Reserved

00

B

5-0

Odd Field

WSS CRC Data

If odd field WSS is enabled and present during NTSC operation, this register is loaded

with the six bits of CRC information on line 20. It is always a “000000” during PAL oper-

ation. Data written to this register is ignored.

000000

B

TABLE 38. WSS_EVEN_A DATA REGISTER

SUB ADDRESS = 27

H

BIT

NO.

FUNCTION

DESCRIPTION

RESET

STATE

7-0

Even Field

WSS Data

If even field WSS is enabled and present, this register is loaded with the first eight bits of

WSS information on line 280, 283, or 336. Bit 0 corresponds to the first bit of WSS infor-

mation. Data written to this register is ignored.

00

H

TABLE 39. WSS_EVEN_B DATA REGISTER

SUB ADDRESS = 28

H

BIT

NO.

FUNCTION

DESCRIPTION

RESET

STATE

15-14

Reserved

00

B

13-8

Even Field

WSS Data

If even field WSS is enabled and present, this register is loaded with the second six bits

of WSS information on line 280, 283, or 336. Data written to this register is ignored.

000000

B

HMP8115

相關PDF資料 |

PDF描述 |

|---|---|

| HMP8115CN | NTSC/PAL Video Decoder |

| HMR100 | Hadware Manual |

| HMR-100 | Hadware Manual |

| HMS188CWHRLP-20 | x8 SRAM |

| HMS188CS-15 | x8 SRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HMP8115CN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8116 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8116CN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117_07 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復。