- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371861 > HMP8115 (Intersil Corporation) NTSC/PAL Video Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | HMP8115 |

| 廠(chǎng)商: | Intersil Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL視頻解碼器 |

| 文件頁(yè)數(shù): | 10/43頁(yè) |

| 文件大小: | 183K |

| 代理商: | HMP8115 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)

10

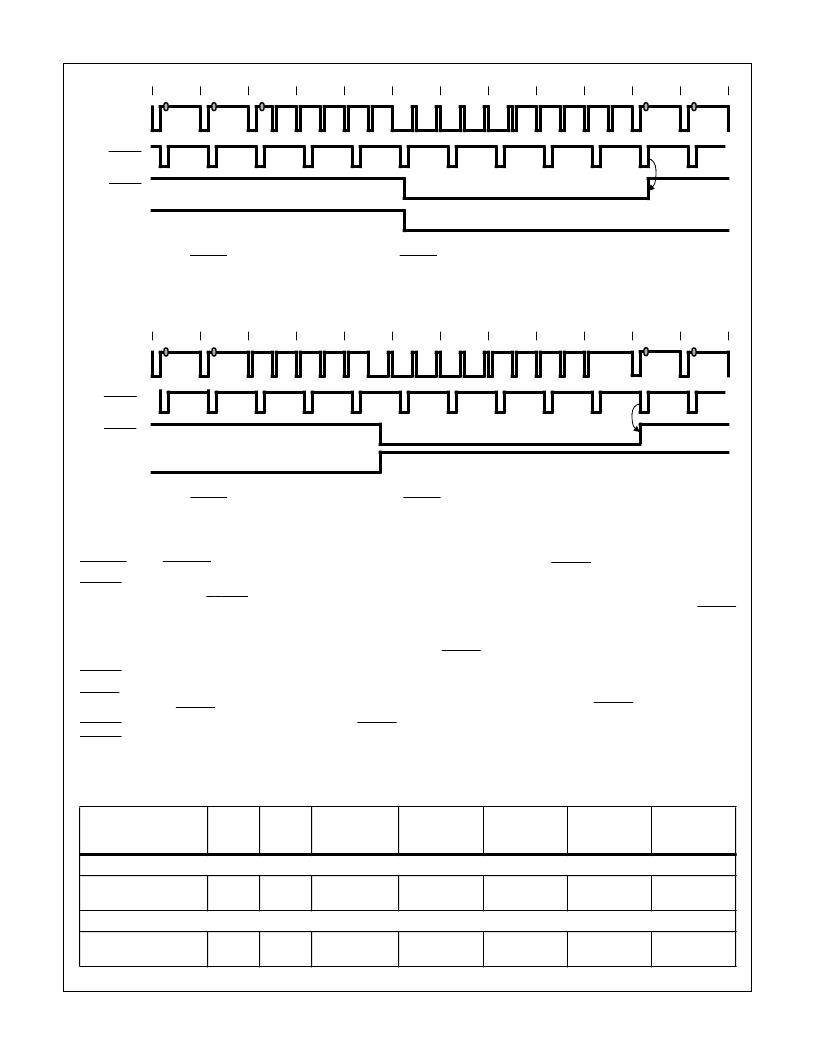

BLANK AND DVALID TIMING

DVALID is asserted when P15-P0 contain valid data. The

timing and behavior of DVALID is dependent on the output

video format and the programmed values for bit 4

(DVLD_DCYC) and bit 5 (DVLD_LTC) of the GENLOCK

CONTROL register 04

H

. Refer to the specific output video

format sections that follow for the specific behavior for

DVALID.

BLANK is used to determine if the HMP8115 is generating

active video data. BLANK should be used in conjunction with

DVALID to capture digital data from the decoder. BLANK,

DVALID and the video data are output after the internal pipe-

line latency and synchronous with the rising edge of CLK2.

During active scan lines BLANK is negated when the hori-

zontal pixel count matches the value in the END H_BLANK

register 32

H

. A count of 00

H

corresponds to the 50% point of

the leading edge of the sync tip after leaving the part. BLANK

is asserted when the horizontal pixel count matches the value

in the START H_BLANK register 31

H

/30

H

. Note that horizon-

tally, BLANK is programmable with two pixel resolution.

START V_BLANK register 34

H

/33

H

and END V_BLANK reg-

ister 35

H

determine which scan lines are blanked for each

field. During inactive scan lines, BLANK is asserted during

the entire scan line. Half-line blanking of the output video

cannot be done. Reference Figure 9 for active video timing

and use Table 2 for typical blanking programming values.

VIDEO

INPUT

VSYNC

FIELD

‘EVEN’ FIELD

NOTE:

5. The trailing edge of VSYNC is 5

±

1 clocks after the trailing edge of HSYNC is to be VMI compatible and to indicate a transition to an odd field.

FIGURE 7. PAL(B,D,G,H,I,N,N

C

) HSYNC, VSYNC AND FIELD TIMING DURING AN EVEN TO ODD FIELD TRANSITION

‘ODD’ FIELD

HSYNC

623

LINE #

624

625

1

2

3

4

5

6

7

622

621

NOTE:

6. The trailing edge of VSYNC is 5

±

1 clocks after the leading edge of HSYNC to be VMI compatible and to indicate a transition to an even field.

FIGURE 8. PAL(B,D,G,H,I,N,N

C

) HSYNC, VSYNC AND FIELD TIMING DURING AN ODD TO EVEN FIELD TRANSITION

VIDEO

INPUT

VSYNC

FIELD

‘ODD’ FIELD

‘EVEN’ FIELD

HSYNC

311

LINE #

312

313

314

315

316

317

318

319

320

310

309

TABLE 2. TYPICAL VALUES FOR HBLANK AND VBLANK REGISTERS

VIDEO STANDARD

(MSB/LSB)

ACTIVE

PIXELS/

LINE

TOTAL

PIXELS/

LINE

LAST

PIXEL

COUNT

START

H_BLANK

(31H/30H)

END

H_BLANK

(32H)

START

V_BLANK

(34H/33H)

END

V_BLANK

(35H)

RECTANGULAR PIXELS

NTSC (M), PAL (M)

PAL (B, D, G, H, I,N, N

C

)

720

720

858

864

857 (0359

H

)

863 (035F

H

)

842 (034A

H

)

852 (0354

H

)

122 (7A

H

)

132 (84

H

)

259 (0103

H

)

310 (0136

H

)

19 (13

H

)

22 (16

H

)

SQUARE PIXELS

NTSC (M), PAL (M)

PAL (B, D, G, H, I,N, N

C

)

640

768

780

944

779 (030B

H

)

943 (03AF

H

)

758 (02F6

H

)

922 (039A

H

)

118 (76

H

)

154 (9A

H

)

259 (0103

H

)

310 (0136

H

)

19 (13

H

)

22 (16

H

)

HMP8115

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMP8115CN | NTSC/PAL Video Decoder |

| HMR100 | Hadware Manual |

| HMR-100 | Hadware Manual |

| HMS188CWHRLP-20 | x8 SRAM |

| HMS188CS-15 | x8 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMP8115CN | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8116 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8116CN | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117_07 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。