- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384404 > HFA3861 (Intersil Corporation) Direct Sequence Spread Spectrum (DSSS) baseband processor(直接序列擴(kuò)頻基帶處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | HFA3861 |

| 廠商: | Intersil Corporation |

| 元件分類: | 基帶處理器 |

| 英文描述: | Direct Sequence Spread Spectrum (DSSS) baseband processor(直接序列擴(kuò)頻基帶處理器) |

| 中文描述: | 直接序列擴(kuò)頻(DSSS)基帶處理器(直接序列擴(kuò)頻基帶處理器) |

| 文件頁(yè)數(shù): | 24/35頁(yè) |

| 文件大?。?/td> | 218K |

| 代理商: | HFA3861 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

24

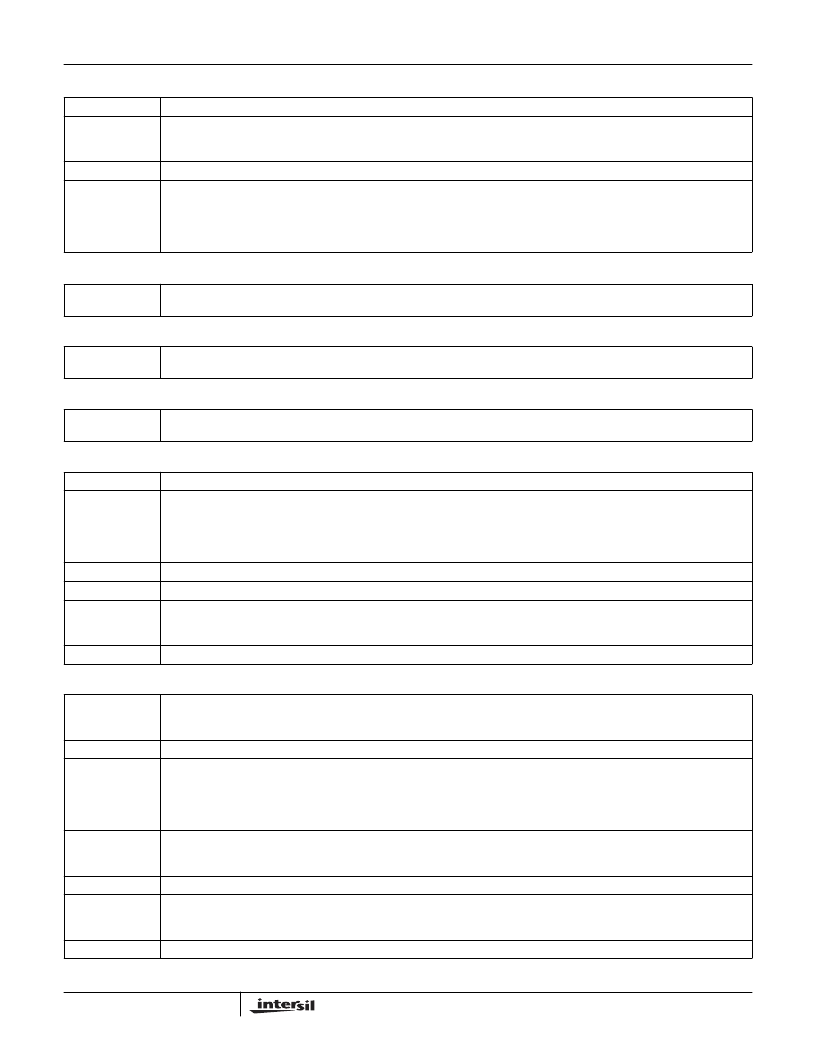

CONFIGURATION REGISTER 5 ADDRESS (0Ah) R/W TX SIGNAL FIELD

Bits 7:4

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

Bits 3

Select preamble mode

0 = Normal, long preamble interoperable with 1 and 2Mbps legacy equipment

1= short preamble and header mode (optional in 802.11)

Bit 2

reserved, must be set to 0

Bits 1:0

TX data Rate. Must be set at least 2

μ

s before needed in TX frame. This selects TX signal field code from the registers above.

00 = DBPSK - 11 chip sequence (1Mbps)

01 = DQPSK - 11 chip sequence (2Mbps)

10 = CCK - 8 chip sequence (5.5Mbps)

11 = CCK - 8 chip sequence (11Mbps)

CONFIGURATION REGISTER 6 ADDRESS (0Ch) R/W TX SERVICE FIELD

Bits 7:0

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions. Bit 7 may be employed

by the MAC in 802.11 situations to resolve an ambiguity in the length field when in the 11Mbps mode.

CONFIGURATION REGISTER 7 ADDRESS (0Eh) R/W TX LENGTH FIELD (HIGH)

Bits 7:0

This 8-bit register contains the higher byte (bits 8-15) of the transmit Length Field described in the Header. This byte combined

with the lower byte indicates the number of microseconds the data packet will take.

CONFIGURATION REGISTER 8 ADDRESS (10h) R/W TX LENGTH FIELD (LOW)

Bits 7:0

This 8-bit register contains the lower byte (bits 0-7) of the transmit Length Field described in the Header. This byte combined

with the higher byte indicates the number of microseconds the data packet will take.

CONFIGURATION REGISTER 9 ADDRESS (12h) R/W TX CONFIGURE

Bit 7

Unused

Bits 6:5

CCA mode

00 - CCA is based only on ED

01 - CCA is based on (CS1 OR CS2)

10 - CCA is based on (ED AND (CS1 OR CS2))

11 - CCA is based on CS2 only

Bit 4

Reserved, must be set to 0

Bit 3

Reserved, must be set to 0

Bit 2:1

TX Antenna Selection

0x = set antenna select pin low during transmit

1x = set antenna select pin high during transmit

Bit 0

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

CONFIGURATION REGISTER 10 ADDRESS (14h) R/W RX CONFIGURE

Bit 7

Acquisition mode

0 - Use CS1 followed by CS2, or two consecutive CS2s

1 - Use only consecutive CS2s

Bit 6

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

Bits 5:4

SFD Time-out values

00 = 56

μ

s

01 = 64

μ

s

10 = 128

μ

s

11 = 144

μ

s

Bit 3

MD_RDY control

0 = After CRC16

1 = After SFD

Bit 2

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

Bit 1

antenna choice for Receive

0 = Antenna select pin low

1 = Antenna select pin high

Bit 0

R/W but not currently used internally, should be set to zero to ensure compatibility with future revisions.

HFA3861

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3861IV | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3925 | 2.4GHz - 2.5GHz 250mW Power Amplifier(2.4GHz - 2.5GHz 250mW 功率放大器) |

| HFA3926 | 2.0GHz - 2.7GHz 250mW Power Amplifier(2.0GHz - 2.7GHz 250mW 功率放大器) |

| HFA3926IA | 2.0GHz - 2.7GHz 250mW Power Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3861A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

| HFA3861AIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

| HFA3861AIN96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

| HFA3861B | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。