- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370499 > HDMP-1546A Fibre Channel Transceiver Chip(光纖通道收發(fā)器芯片) PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1546A |

| 英文描述: | Fibre Channel Transceiver Chip(光纖通道收發(fā)器芯片) |

| 中文描述: | 光纖通道收發(fā)器芯片(光纖通道收發(fā)器芯片) |

| 文件頁(yè)數(shù): | 12/16頁(yè) |

| 文件大?。?/td> | 246K |

| 代理商: | HDMP-1546A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

12

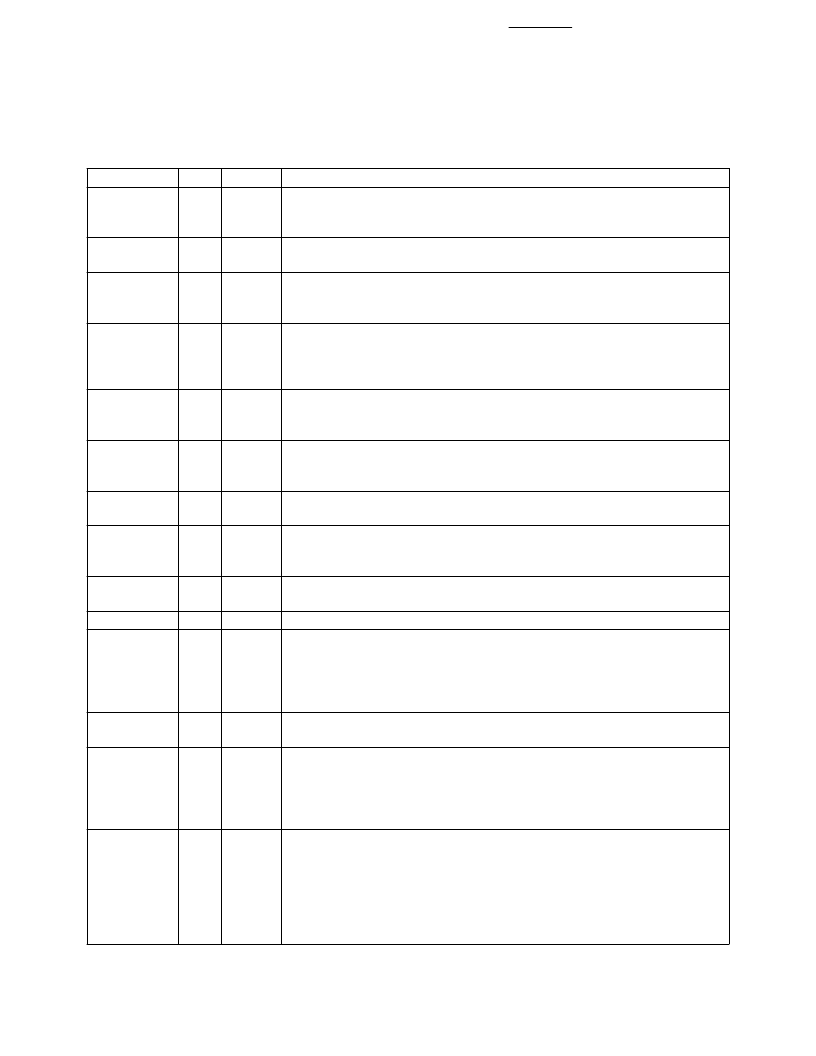

TRx I/O Definition

Name

BYTSYNC

Pin

47

Type

O-TTL

Signal

Byte Sync Output:

An active high output. Used to indicate detection of

a comma character (0011111XXX). It is only active when ENBYTSYNC

is enabled.

Serial Data Inputs:

High-speed inputs. Serial data is accepted from the

±

DIN inputs when LOOPEN is low.

HS_OUT

Serial Data Outputs:

High-speed outputs. These lines are active when

LOOPEN is set low. When LOOPEN is set high, these outputs are held

static at logic level 1.

I-TTL

Enable Byte Sync Input:

When high, turns on the internal byte sync

function to allow clock synchronization to a comma character

(0011111XXX). When the line is low, the function is disabled and

will not reset registers and clocks, or strobe the BYTSYNC line.

S

Logic Ground:

Normally 0 volts. This ground is used for internal PECL

logic. It should be isolated from the noisy TTL ground as well as possible.

-DIN

+DIN

-DOUT

+DOUT

52

54

61

62

HS_IN

ENBYTSYNC

24

GND

21

25

58

1

14

56

51

*GND

This pin is bonded to an isolated pad and has no functionality. However,

it is recommended that this pin be connected to GND in order to conform

with the X3T11 “10-bit specification,” and to help dissipate heat.

Analog Ground:

Normally 0 volts. Used to provide a clean ground

plane for the receiver PLL and high-speed analog cells.

TTL Receiver Ground:

Normally 0 volts. Used for the TTL output cells

of the receiver section.

GND_RXA

S

GND_RXTTL

32

33

46

15

S

GND_TXA

S

Analog Ground:

Normally 0 volts. Used to provide a clean ground plane

for the PLL and high-speed analog cells.

Ground:

Normally 0 volts.

Loopback Enable Input:

When set high, the high-speed serial signal is

internally wrapped from the transmitter’s serial loopback outputs back

to the receiver’s loopback inputs. Also, when in loopback mode, the

±

DOUT outputs are held static at logic level 1. When set low,

±

DOUT

outputs and

±

DIN inputs are active.

This pin is connected to an isolated pad and has no functionality. It can be

left open, however, TTL levels can also be applied to this pin.

Receiver Byte Clocks:

The receiver section recovers two 53.125 MHz

receive byte clocks. These two clocks are 180 degrees out of phase.

The receiver parallel data outputs are alternatively clocked on the

rising edge of these clocks. The rising edge of RBC1 aligns with the

output of the comma character (for byte alignment) when detected.

Reference Clock and Transmit Byte Clock:

A 106.25 MHz clock

supplied by the host system. The transmitter section accepts this signal

as the frequency reference clock. It is multiplied by 10 to generate the

serial bit clock and other internal clocks. The transmit side also uses this

clock as the transmit byte clock for the incoming parallel data

TX[0]..TX[9]. It also serves as the reference clock for the receive

portion of the transceiver.

GND_TXHS

LOOPEN

64

19

S

I-TTL

*N/C

27

RBC1

RBC0

30

31

O-TTL

REFCLK

22

I-TTL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1536A | Fibre Channel Transceiver Chip(光纖通道收發(fā)器芯片) |

| HDMP-1636 | Software |

| HDMP-1646 | Gigabit Ethernet Transceiver Chip |

| HDMP-1646A | Gigabit Ethernet Serialize/Deserialize (SerDes) IC(千兆位以太網(wǎng)串行器/解串行器) |

| HDMP-1636A | Gigabit Ethernet Serialize/Deserialize (SerDes) IC(千兆位以太網(wǎng)串行器/解串行器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1636 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Gigabit Ethernet Transceiver Chip |

| HDMP-1636A | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Gigabit Ethernet and Fibre Channel SerDes ICs |

| HDMP-1636AG | 制造商:PMC-Sierra 功能描述:1.06/1.25 GB SerDes for GB EOL301107 |

| HDMP-1637A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.25 GBd SerDes Circuit with Differential PECL Clock Inputs for Gigabit Ethernet Applications |

| HDMP-1638 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Gigabit Ethernet Transceiver Chip with Dual Serial I/O and Differential PECL Clock Inputs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。