- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1512 Fibre Channel Transmitter Chipset(光纖通道傳送芯片) PDF資料下載

參數(shù)資料

| 型號: | HDMP-1512 |

| 英文描述: | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| 中文描述: | 光纖通道發(fā)射器芯片組(光纖通道傳送芯片) |

| 文件頁數(shù): | 2/26頁 |

| 文件大小: | 284K |

| 代理商: | HDMP-1512 |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

2

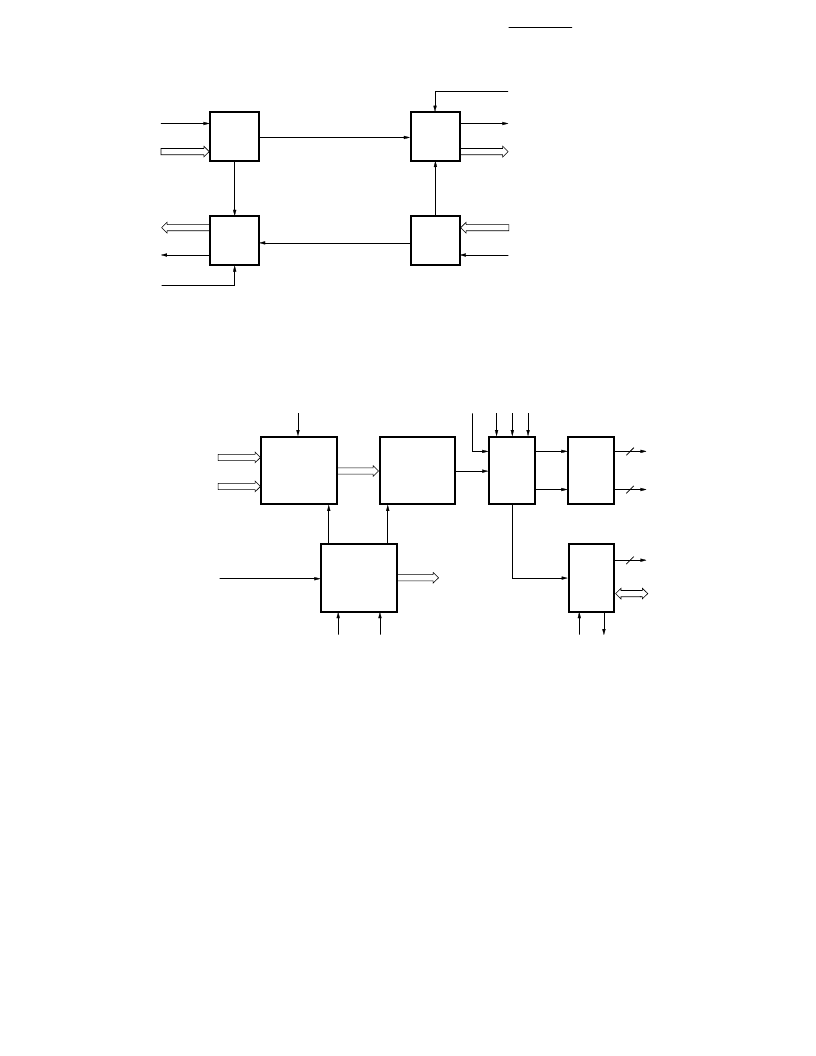

Figure 2. HDMP-1512 (Tx) Block Diagram.

TTL INTERFACE

AND

INPUT LATCH

DATA BYTE 1

Tx [10:19]

±

DATA BYTE 0

Tx [00:09]

FRAME

MULTIPLEXER

10

10

20

I/O

SELECT

CABLE

DRIVERS

± LOUT

± SO

PLL/CLOCK

GENERATOR

TBC

LASER

DRIVER

INTERNAL

CLOCKS

2

2

± LZOUT

2

LASER

CONTROLS

T

T

E

P

S

-

F

-

Transmitter Operation

The block diagram of the HDMP-

1512 transmitter is shown in

Figure 2. The basic functions of

the transmitter chip are the TTL

Interface and Input Latch, Frame

Multiplexing, Input/Output

selection, cable drivers, Laser

Driver, and monolithic Phase

Locked loop clock generator. The

actual operation of each function

changes slightly, according to the

desired configuration and option

settings. Figures 18 and 19 show

schematically how to terminate

each pin on the HDMP-1512

when used in systems incorporat-

ing either copper or fiber media.

There are two main modes of

operation for the transmitter

chip, both are based on the

selected baud rate. The baud rate

is controlled by the appropriate

setting of the SPDSEL pin, #67.

When this pin is set low, the

transmitter operates at a serial

rate of 531.25 Mbaud. When pin

#67 is set high the transmitter

operates at a serial rate of 1062.5

Mbaud. As such, the two main

modes of operation are the

531.25 Mbaud mode and the

1062.5 Mbaud mode.

The transmitter does not encode

the applied data. It assumes the

data is pre-encoded using the

8B/10B encoding scheme as

defined in ANSI X3.230-1994.

The TTL input interface receives

data at the standard TTL levels

specified in the dc Electrical

Specification table. The internal

phase locked loop (PLL) locks to

the transmit byte clock, TBC.

TBC is supplied to the transmitter

chip by the sending system. TBC

should be a 53.125 MHz clock

(

±

100 ppm) as defined in

X3.230-1994. Once the PLL has

locked to TBC, all the clocks used

by the transmitter are generated

by the internal clock generator.

CLOCK

Tx

Rx

ENCODED DATA

CLOCK

ENCODED DATA

REF CLOCK

Rx

Tx

CLOCK

ENCODED DATA

CLOCK

ENCODED DATA

REF CLOCK

SERIAL LINK

SERIAL LINK

Figure 1. Point-to-Point Data Link.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

| HDMP-1526 | Transistor Diode Kit;Contents Of Kit:Transistor/Diode Kit |

| HDMP-1536 | Fibre Channel Transceiver Chip |

| HDMP-1546 | Fibre Channel Transceiver Chip |

| HDMP-1546A | Fibre Channel Transceiver Chip(光纖通道收發(fā)器芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1514 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transmitter and Receiver Chipset |

| HDMP1526 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| HDMP-1526 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transceiver Chip |

| HDMP-1536 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transceiver Chip |

| HDMP-1536A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fiber-Optic Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。