- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1512 Fibre Channel Transmitter Chipset(光纖通道傳送芯片) PDF資料下載

參數(shù)資料

| 型號: | HDMP-1512 |

| 英文描述: | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| 中文描述: | 光纖通道發(fā)射器芯片組(光纖通道傳送芯片) |

| 文件頁數(shù): | 14/26頁 |

| 文件大?。?/td> | 284K |

| 代理商: | HDMP-1512 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

14

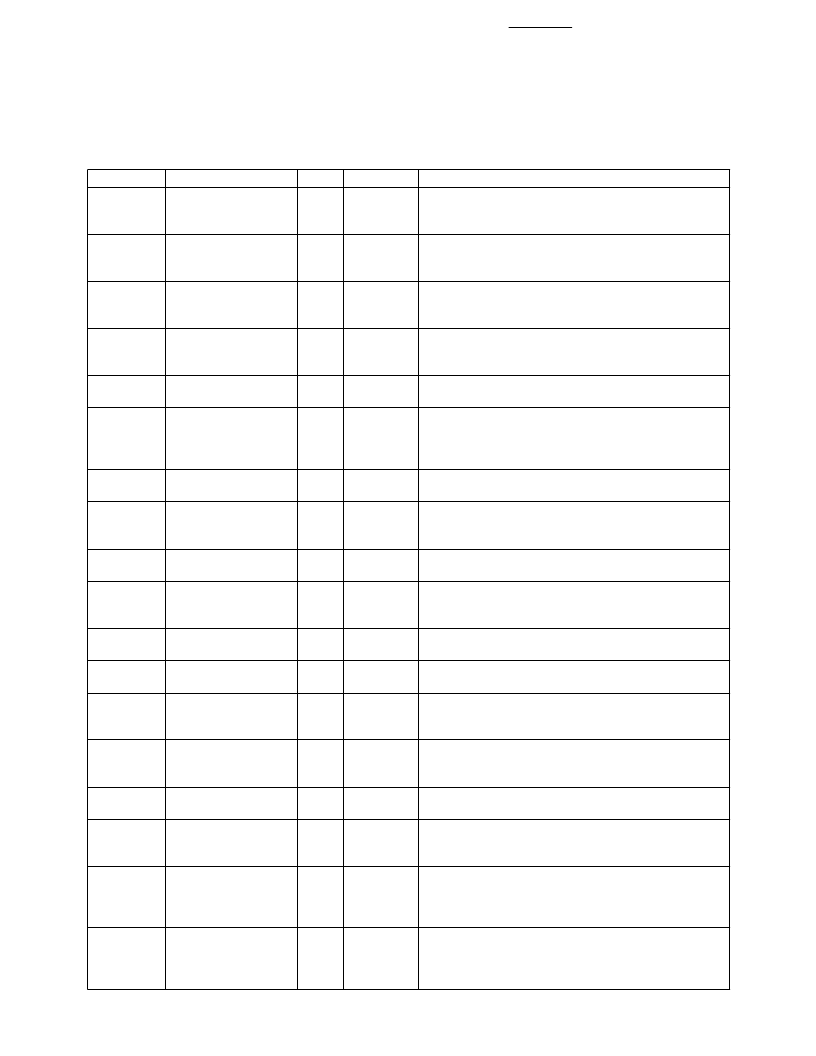

HDMP-1512 (Tx), Signal Definitions

Symbol

CAP0[A:B]

Signal Name

Loop Filter Capacitor

Pins [79,80]

I/O

C

Logic Type

Description

PLL filter capacitor should be connected from pins

79 and 80 to pins 1 and 2 (typical value = 0.01

μ

F).

See Figures 18, 19, 20, and 21.

PLL filter capacitor should be connected from pins

79 and 80 to pins 1 and 2 (typical value = 0.01

μ

F).

See Figures 18, 19, 20, and 21.

An active low input, causes the transmitter to

internally generate the positive disparity K28.5 byte

(0011111010) for transmission.

An active low input, selects the TBC inputs to be used

as the serial clock, bypassing the PLL. Used mainly

for testing.

Works in conjunction with TS1 and TS2 to specify

input and output ports.

Indicates the laser output level has moved outside of

the window detector set boundary and the laser test

capacitor (LZTC) has discharged to a fault level. This

output is reset by the -LZON pin.

Normally 0 volts. Used to provide a clean ground plane

for the critical PLL and high speed analog cells.

Normally 0 volts. Used for all internal PECL logic.

Should be completely isolated from the noisy TTL

ground.

Normally 0 volts. Used for all laser circuitry.

CAP1[A:B]

Loop Filter Capacitor

Pins [1,2]

C

-COMGEN

Comma Generate

Pin [32]

Input

TTL

-ECLKSEL

External Clock Select

Pin [69]

Input

TTL

EWRAP

Enable Wrap

Pin [71]

Laser Fault Indicator

Pin [29]

Input

TTL

FAULT

Output

TTL

GND_A

Analog Ground

Pins [3,4]

Logic Ground

Pins [31,35,70,74]

S

GND_LOG

S

GND_LZ

Laser Ground

Pins [25,26]

Laser High Speed

Ground

Pins [10,18]

TTL Ground

Pins [39,40,65,66]

Local Serial Data

Pins [8,9]

Laser Bandgap Test

Point

Pin [28]

Laser Current Source

Emitter

Pin [14]

Laser DC Drive

Pin [21]

Laser Driver Serial

Output

Pins [19,20]

Laser Monitor Diode

Feedback

Pin [22]

S

GND_LZHS

S

Normally 0 volts.

GND_TTL

S

Normally 0 volts. Used for all TTL I/O buffer cells.

±

LOUT

Output

BLL

High speed data port, typically connected to the

±

LIN

port on the local receiver during serial wrap mode.

This pin is internally set to 2.3 VDC and normally

should connect to one terminal of the laser DC bias

resistor (pot1 Figure 3).

Used to set the bias current of the AC laser driver.

Typical use is shown in Figure 3 where pot2 is used to

set the laser modulation depth.

Used to control the laser diode DC bias (Figure 3).

LZBTP

C

LZCSE

C

LZDC

C

±

LZOUT

C

AC driver to the laser diode. The outputs should be AC

coupled to the laser bias circuit.

LZMDF

C

Connects to the laser monitor diode and one terminal of

the laser DC bias resistor (pot1). Under normal

operating conditions, the voltage on this pin will

be 1.85 V.

The laser diode is turned on (active low) or off (high)

with this input. In the off state the capacitor on pin

LZTC charges, resetting the window

detector (Figure 3).

-LZON

Laser Control and

Reset

Pin [30]

Input

TTL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

| HDMP-1526 | Transistor Diode Kit;Contents Of Kit:Transistor/Diode Kit |

| HDMP-1536 | Fibre Channel Transceiver Chip |

| HDMP-1546 | Fibre Channel Transceiver Chip |

| HDMP-1546A | Fibre Channel Transceiver Chip(光纖通道收發(fā)器芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1514 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transmitter and Receiver Chipset |

| HDMP1526 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| HDMP-1526 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transceiver Chip |

| HDMP-1536 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transceiver Chip |

| HDMP-1536A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Fiber-Optic Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。