- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383053 > GS881E18T-100 (GSI TECHNOLOGY) 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs PDF資料下載

參數(shù)資料

| 型號: | GS881E18T-100 |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| 中文描述: | 512K X 18 CACHE SRAM, 12 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數(shù): | 23/34頁 |

| 文件大?。?/td> | 487K |

| 代理商: | GS881E18T-100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

Rev: 1.10 9/2000

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com

23/34

2000, Giga Semconductor, Inc.

Preliminary

GS881E18/36T-11/11.5/100/80/66

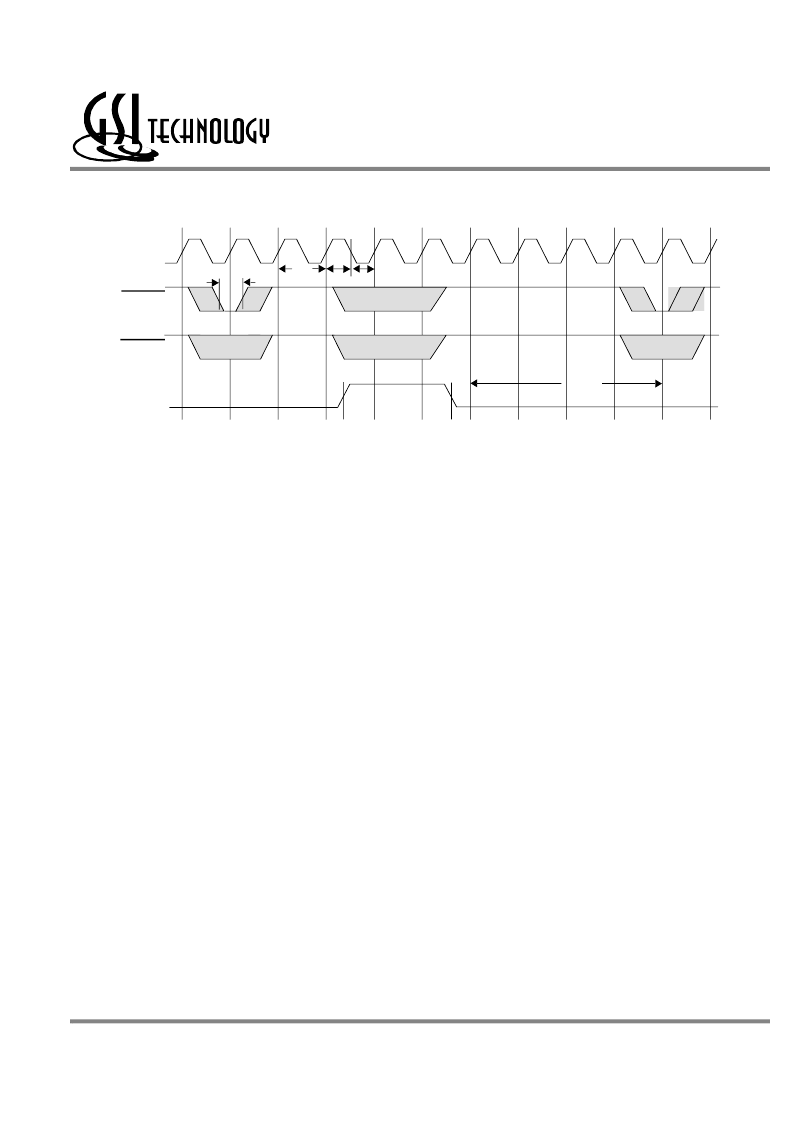

Sleep Mode Timing Diagram

Application Tips

Single and Dual Cycle Deselect

SCD devices force the use of “dummy read cycles” (read cycles that are launched normally but that are ended with the output

drivers inactive) in a fully synchronous environment. Dummy read cycles waste performance but their use usually assures there

will be no bus contention in transitions from reads to writes or between banks of RAMs. DCD SRAMs do not waste bandwidth on

dummy cycles and are logically simpler to manage in a multiple bank application (wait states need not be inserted at bank address

boundary crossings) but greater care must be exercised to avoid excessive bus contention.

JTAG Port Operation

Overview

The JTAG Port on this RAM operates in a manner consistent with IEEE Standard 1149.1-1990, a serial boundary scan interface

standard (commonly referred to as JTAG), but does not implement all of the functions required for 1149.1 compliance. Some

functions have been modified or eliminated because they can slow the RAM. Nevertheless, the RAM supports 1149.1-1990 TAP

(Test Access Port) Controller architecture, and can be expected to function in a manner that does not conflict with the operation of

Standard 1149.1 compliant devices. The JTAG Port interfaces with conventional TTL / CMOS logic level signaling.

Disabling the JTAG Port

It is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless

clocked. TCK, TDI, and TMS are designed with internal pull-up circuits. To assure normal operation of the RAM with the JTAG

Port unused, TCK, TDI, and TMS may be left floating or tied to either V

DD

or V

SS

. TDO should be left unconnected.

CK

ADSP

ADSC

tH

tKH tKL

tKC

tS

ZZ

tZZR

tZZH

tZZS

~

~

~

~

Snooze

相關PDF資料 |

PDF描述 |

|---|---|

| GS881E18T-100I | 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11 | 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11.5 | 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11.5I | 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11I | 512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS881E18T-100I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11.5 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11.5I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

| GS881E18T-11I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:512K x 18, 256K x 36 ByteSafe 8Mb Sync Burst SRAMs |

發(fā)布緊急采購,3分鐘左右您將得到回復。