- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385323 > GS832418C-250 (GSI TECHNOLOGY) 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs PDF資料下載

參數(shù)資料

| 型號: | GS832418C-250 |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| 中文描述: | 2M X 18 CACHE SRAM, 6 ns, PBGA209 |

| 封裝: | 14 X 22 MM, 1 MM PITCH, BGA-209 |

| 文件頁數(shù): | 5/46頁 |

| 文件大?。?/td> | 1149K |

| 代理商: | GS832418C-250 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

Rev: 1.00 10/2001

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

5/46

2001, Giga Semiconductor, Inc.

Preliminary

GS832418(B/C)/GS832436(B/C)/GS832472(C)

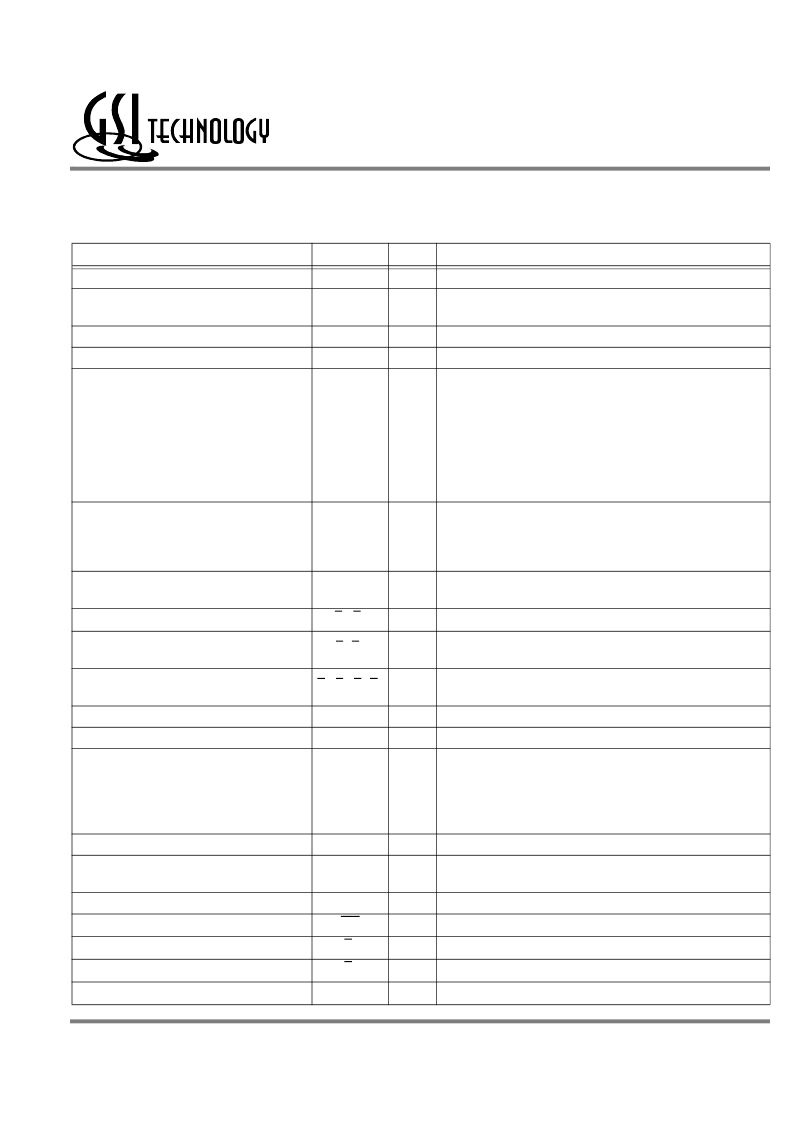

GS832418/36/72 209-Bump BGA Pin Description

Pin Location

W6, V6

Symbol

A

0

, A

1

Type

I

Description

Address field LSBs and Address Counter Preset Inputs.

W7, W5, V9, V8, V7, V5, V4, V3, U8, U7, U6,

U5, U4, A3, B7, A9, U9

B5

C7

L11, M11, N11, P11, L10, M10, N10, P10, R10

A10, B10, C10, D10, A11, B11, C11, D11, E11

J1, H1, G1, F1, J2, H2, G2, F2, E2

W2, V2, U2, T2, W1, V1, U1, T1, R1

W10, V10, U10, T10, W11, V11, U11, T11, R11

J11, H11, G11, F11, J10, H10, G10, F10, E10

A2, B2, C2, D2, A1, B1, C1, D1, E1

L1, M1, N1, P1, L2, M2, N2, P2, R2

L11, M11, N11, P11, L10, M10, N10, P10, R10

A10, B10, C10, D10, A11, B11, C11, D11, E11

J1, H1, G1, F1, J2, H2, G2, F2, E2

W2, V2, U2, T2, W1, V1, U1, T1, R1

L11, M11, N11, P11, L10, M10, N10, P10, R10

J1, H1, G1, F1, J2, H2, G2, F2, E2

An

I

Address Inputs

A

19

A

20

I

I

Address Inputs (x36/x18 Versions)

Address Inputs (x18 Version)

DQ

A1

–

DQ

A9

DQ

B1

–

DQ

B9

DQ

C1

–

DQ

C9

DQ

D1

–

DQ

D9

DQ

E1

–

DQ

E9

DQ

F1

–

DQ

F9

DQ

G1

–

DQ

G9

DQ

H1

–

DQ

H9

DQ

A1

–

DQ

A9

DQ

B1

–

DQ

B9

DQ

C1

–

DQ

C9

DQ

D1

–

DQ

D9

DQ

A1

–

DQ

A9

DQ

B1

–

DQ

B9

I/O

Data Input and Output pins (x72 Version)

I/O

Data Input and Output pins (x36 Version)

I/O

Data Input and Output pins (x18 Version)

C9, B8

B

A

, B

B

I

Byte Write Enable for DQ

A

, DQ

B

I/Os; active low

B3, C4

B

C

,B

D

I

Byte Write Enable for DQ

C

, DQ

D

I/Os; active low

(x72/x36 Versions)

Byte Write Enable for DQ

E

, DQ

F

, DQ

G

, DQ

H

I/Os; active low

(x72 Version)

No Connect (x72 Version)

No Connect (x72/x36 Versions)

C8, B9, B4, C3

B

E

, B

F

, B

G

,B

H

I

B5

C7

NC

NC

—

—

W10, V10, U10, T10, W11, V11, U11, T11, R11

J11, H11, G11, F11, J10, H10, G10, F10, E10

A2, B2, C2, D2, A1, B1, C1, D1, E1

L1, M1, N1, P1, L2, M2, N2, P2, R2, C8, B9,

B4, C3

B3, C4

C5, D4, D5, D8, K1, K2, K4, K8, K9, K10, K11,

T4, T5, T7, T8, U3

K3

NC

—

No Connect (x36/x18 Versions)

NC

—

No Connect (x18 Version)

NC

—

No Connect

CK

I

Clock Input Signal; active high

D7

GW

I

Global Write Enable—Writes all bytes; active low

C6

E

1

I

Chip Enable; active low

A8

E

3

I

Chip Enable; active low (x72/x36 Versions)

A4

E

2

I

Chip Enable; active high (x72/x36 Versions)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS832418C-250I | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS832436B-133 | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS832436B-133I | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS832436B-150 | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS832436B-150I | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8324Z36B-133 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 2.5V/3.3V 36MBIT 1MX36 10NS/4NS 119FBGA - Trays |

| GS8324Z36B-200I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 2.5V/3.3V 36MBIT 1MX36 7.5NS/3NS 119FBGA - Trays |

| GS8324Z72C200 | 制造商:G.S.I. 功能描述: |

| GS8342D06BD-350 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8342D06BD-500 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。