- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄375759 > FC80960HD50SL2GM (INTEL CORP) 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor PDF資料下載

參數(shù)資料

| 型號(hào): | FC80960HD50SL2GM |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| 中文描述: | 32-BIT, 50 MHz, RISC PROCESSOR, PQFP208 |

| 封裝: | PLASTIC, QFP-208 |

| 文件頁(yè)數(shù): | 15/102頁(yè) |

| 文件大?。?/td> | 828K |

| 代理商: | FC80960HD50SL2GM |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

80960HA/HD/HT

Advance Information

Datasheet

9

SUP

O

H(Z)

B(Z)

R(1)

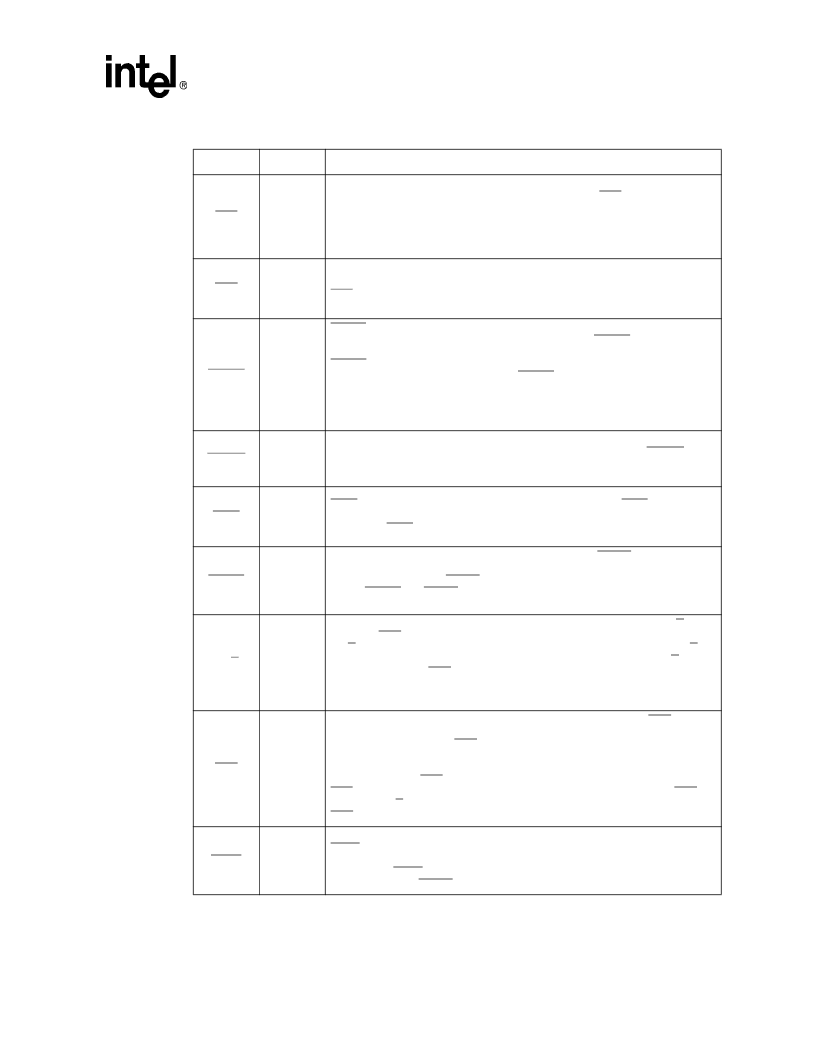

SUPERVISOR ACCESS

indicates whether the current bus access originates from

a request issued while in supervisor mode or user mode. SUP can be used by the

memory subsystem to isolate supervisor code and data structures from

non-supervisor access.

0 = Supervisor Mode

1 = User Mode

ADS

O

H(Z)

B(Z)

R(1)

ADDRESS STROBE

indicates a valid address and the start of a new bus access.

ADS is asserted for the first clock of a bus access.

READY

I

S(L)

READY

, when enabled for a memory region, is asserted by the memory

subsystem to indicate the completion of a data transfer. READY is used to

indicate that read data on the bus is valid, or that a write transfer has completed.

READY works in conjunction with the internal wait state generator to

accommodate various memory speeds. READY is sampled after any programmed

wait states:

During each data cycle of a burst access

During the data cycle of a non-burst access

BTERM

I

S(L)

BURST TERMINATE

, when enabled for a memory region, is asserted by the

memory subsystem to terminate a burst access in progress. When BTERM is

asserted, the current burst access is terminated and another address cycle

occurs.

WAIT

O

H(Z)

B(Z)

R(1)

WAIT

indicates the status of the internal wait-state generator. WAIT is asserted

when the internal wait state generator generates N

, N

, N

WDD

and N

RDD

wait states. WAIT can be used to derive a write data strobe.

BLAST

O

H(Z)

B(Z)

R(1)

BURST LAST

indicates the last transfer in a bus access. BLAST is asserted in the

last data transfer of burst and non-burst accesses after the internal wait-state

generator reaches zero. BLAST remains active as long as wait states are inserted

via the READY pin. BLAST becomes inactive after the final data transfer in a bus

cycle.

DT/R

O

H(Z)

B(Z)

R(0)

DATA TRANSMIT/RECEIVE

indicates direction for data transceivers. DT/R is

used with DEN to provide control for data transceivers connected to the data bus.

DT/R is driven low to indicate the processor expects data (a read cycle). DT/R is

driven high when the processor is “transmitting” data (a store cycle). DT/R only

changes state when DEN is high.

0 = Data Receive

1 = Data Transmit

DEN

O

H(Z)

B(Z)

R(1)

DATA ENABLE

indicates data transfer cycles during a bus access. DEN is

asserted at the start of the first data cycle in a bus access and de-asserted at the

end of the last data cycle. DEN remains asserted for an entire bus request, even

when that request spans several bus accesses. For example, a ldq instruction

starting at an unaligned quad word boundary is one bus request spanning at least

two bus accesses. DEN remains asserted throughout all the accesses (including

ADS states) and de-asserts when the Iqd instruction request is satisfied. DEN is

used with DT/R to provide control for data transceivers connected to the data bus.

DEN remains asserted for sequential reads from pipelined memory regions.

LOCK

O

H(Z)

B(Z)

R(1)

BUS LOCK

indicates that an atomic read-modify-write operation is in progress.

LOCK may be used by the memory subsystem to prevent external agents from

accessing memory that is currently involved in an atomic operation (e.g., a

semaphore). LOCK is asserted in the first clock of an atomic operation and

de-asserted when BLAST is deasserted in the last bus cycle.

Table 7.

80960Hx Processor Family Pin Descriptions (Sheet 2 of 4)

Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FC80960HD66SL2GN | AC 3C 3#16S PIN RECP |

| FC80960HD80SL2LZ | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FC80960HT60SL2G2 | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FC80960HT75SL2GT | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FC80960HA25SL2GU | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FC80960HD66SL2GN | 功能描述:IC MPU I960HD 3V 66MHZ 208-SQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤(pán) |

| FC80960HD80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| FC80960HD80SL2LZ | 功能描述:IC I960HD 3.3V 80MHZ 208QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤(pán) |

| FC80960HT60SL2G2 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FC80960HT75 S L2GT | 制造商:Intel 功能描述:MPU i960? Processor RISC 32-Bit 75MHz 208-Pin PQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。