- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376836 > DP8441 PDF資料下載

參數(shù)資料

| 型號(hào): | DP8441 |

| 文件頁數(shù): | 10/46頁 |

| 文件大小: | 644K |

| 代理商: | DP8441 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

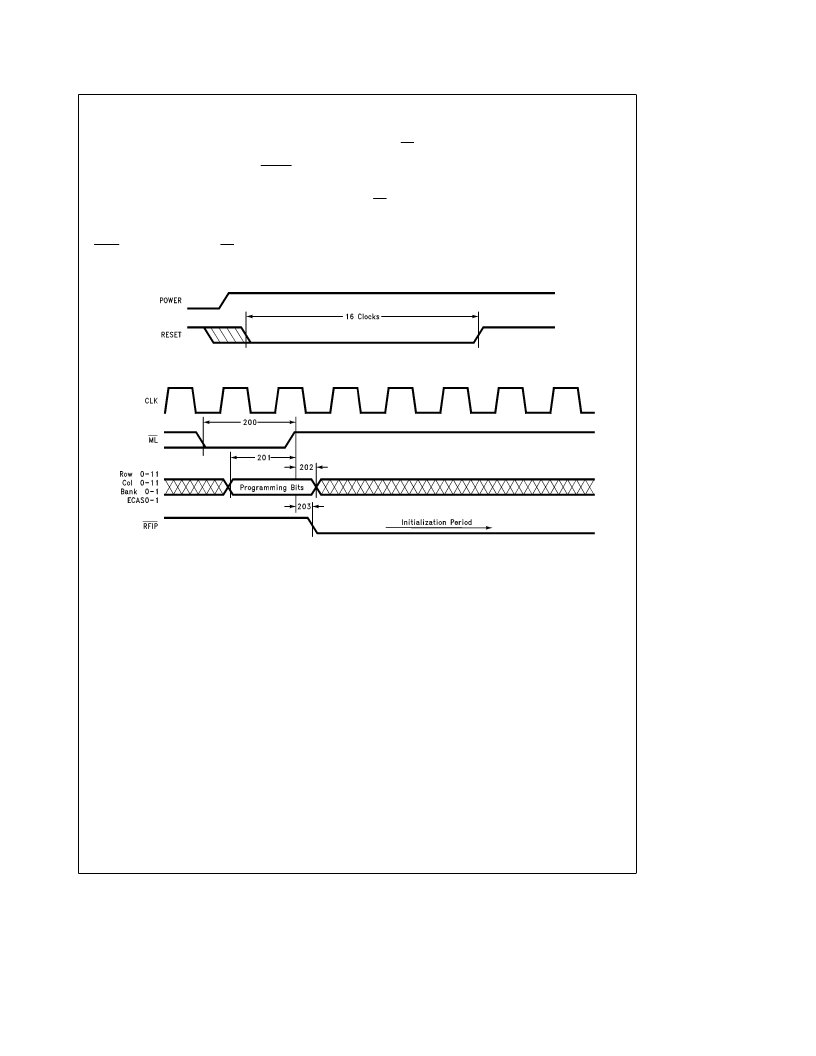

4.0 Programming and Resetting

4.1 RESET

After power up, the DP8440/41 must be reset and pro-

grammed before it can be used to access the DRAM. Reset

is accomplished by asserting the input RESET for at least

16 positive edges of CLK after V

CC

stabilizes. After reset,

the part can be programmed.

4.2 PROGRAMMING

Programming is accomplished by presenting a valid pro-

gramming selection on the row, column, bank selects and

ECAS inputs and toggling the ML input from low to high.

When ML goes high the part is programmed. After the first

programming after a reset the part will enter a 60 ms initiali-

zation period. During this period the controller will refresh

the memory, so further DRAM warm up cycles are not nec-

essary. The user can program the part on the fly by pulsing

ML low and high (provided that no refresh is in progress)

while a valid programming selection is on the address bus.

The part will not enter the initialization period when it is only

re-programmed.

TL/F/11718–4

FIGURE 5. Reset

TL/F/11718–5

FIGURE 6. Programming

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DP84412J | DRAM Controller |

| DP84412N | DRAM Controller |

| DP8441VLJ | DRAM Controller |

| DP84422BN | DRAM Controller |

| DP84422J | DRAM Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DP84412J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84412J/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84412N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84412N/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84412N/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。