- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379806 > CD40105 (Intersil Corporation) CMOS FIFO Register PDF資料下載

參數(shù)資料

| 型號: | CD40105 |

| 廠商: | Intersil Corporation |

| 英文描述: | CMOS FIFO Register |

| 中文描述: | FIFO寄存器的CMOS |

| 文件頁數(shù): | 6/10頁 |

| 文件大?。?/td> | 116K |

| 代理商: | CD40105 |

7-1322

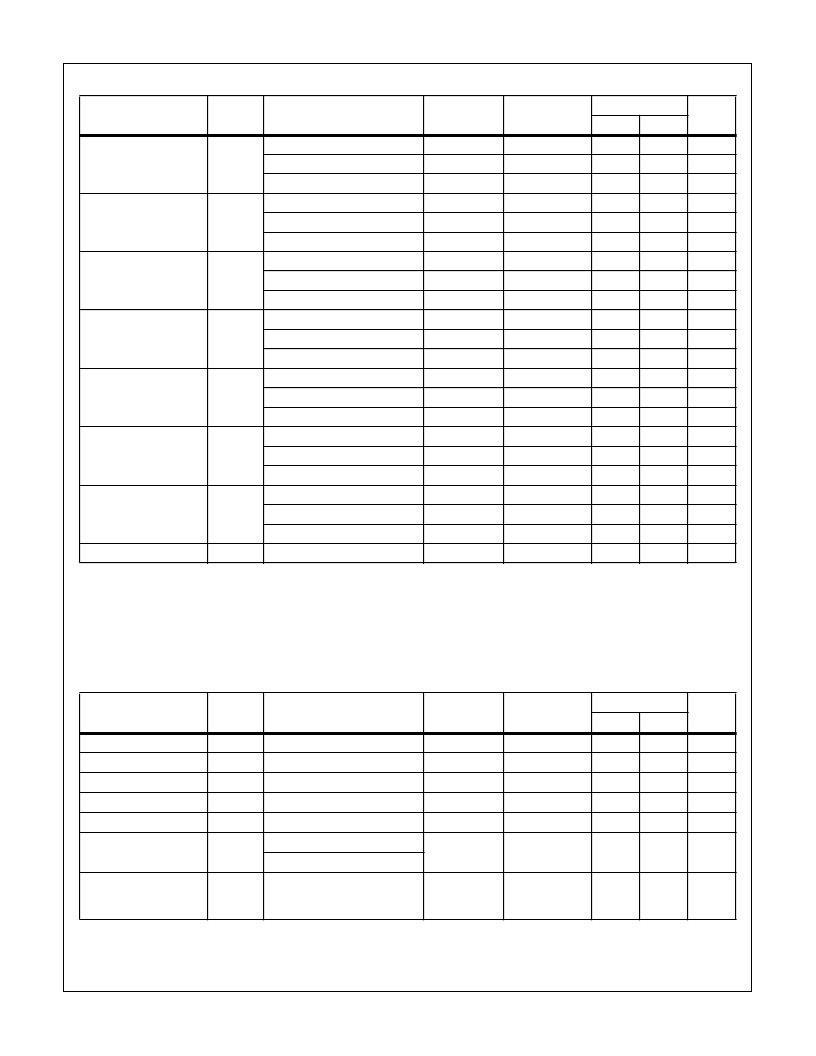

Specifications CD40105BMS

Minimum Master Reset

Pulse Width

TWH

VDD = 5V

1, 2, 3

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

-

200

ns

VDD = 10V

1, 2, 3

-

90

ns

VDD = 15V

1, 2, 3

-

60

ns

Data-In Ready Pulse

Width

TWL

VDD = 5V

1, 2, 3

-

520

ns

VDD = 10V

1, 2, 3

-

200

ns

VDD = 15V

1, 2, 3

-

140

ns

Data-Out Ready Pulse

Width

TWL

VDD = 5V

1, 2, 3

-

440

ns

VDD = 10V

1, 2, 3

-

180

ns

VDD = 15V

1, 2, 3

-

130

ns

Minimum Shift Out Pulse

Width

TWL

VDD = 5V

1, 2, 3

-

180

ns

VDD = 10V

1, 2, 3

-

75

ns

VDD = 15V

1, 2, 3

-

55

ns

Minimum Data Setup

Time

TSU

VDD = 5V

1, 2, 3

-

0

ns

VDD = 10V

1, 2, 3

-

0

ns

VDD = 15V

1, 2, 3

-

0

ns

Minimum Data Hold Time

TH

VDD = 5V

1, 2, 3

-

350

ns

VDD = 10V

1, 2, 3

-

150

ns

VDD = 15V

1, 2, 3

-

120

ns

Minimum Shift In Pulse

Width

TW

VDD = 5V

1, 2, 3

-

200

ns

VDD = 10V

1, 2, 3

-

80

ns

VDD = 15V

1, 2, 3

-

60

ns

Input Capacitance

CIN

Any Input

1, 2

-

7.5

pF

NOTES:

1. All voltages referenced to device GND.

2. The parameters listed on Table 3 are controlled via design or process and are not directly tested. These parameters are characterized

on initial design release and upon design changes which would affect these characteristics.

3. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

4. CL = 50pF, RL = 1K, Input TR, TF < 20ns.

TABLE 4. POST IRRADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER

SYMBOL

CONDITIONS

NOTES

TEMPERATURE

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

+25

o

C

LIMITS

UNITS

MIN

MAX

Supply Current

IDD

VDD = 20V, VIN = VDD or GND

1, 4

-

25

μ

A

N Threshold Voltage

VNTH

VDD = 10V, ISS = -10

μ

A

1, 4

-2.8

-0.2

V

N Threshold Voltage Delta

VTN

VDD = 10V, ISS = -10

μ

A

1, 4

-

±

1

V

P Threshold Voltage

VTP

VSS = 0V, IDD = 10

μ

A

1, 4

0.2

2.8

V

P Threshold Voltage Delta

VTP

VSS = 0V, IDD = 10

μ

A

1, 4

-

±

1

V

Functional

F

VDD = 18V, VIN = VDD or GND

1

VOH >

VDD/2

VOL <

VDD/2

V

VDD = 3V, VIN = VDD or GND

Propagation Delay Time

TPHL

TPLH

VDD = 5V

1, 2, 3, 4

+25

o

C

-

1.35 x

+25

o

C

Limit

ns

NOTES: 1. All voltages referenced to device GND.

2. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

3. See Table 2 for +25

o

C limit.

4. Read and Record

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

PARAMETER

SYMBOL

CONDITIONS

NOTES

TEMPERATURE

LIMITS

UNITS

MIN

MAX

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD40105BMS | CMOS FIFO Register(CMOS 先進(jìn)先出寄存器) |

| CD40106BC | Hex Schmitt Trigger(六施密特觸發(fā)器) |

| CD40106BMJ | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 |

| CD40106 | CMOS HEX SCHMITT TRIGGERS |

| CD40106BMN | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-SSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD40105B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:CMOS FIFO REGISTER |

| CD40105BD | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CD40105BDMSR | 制造商:Intersil Corporation 功能描述:FIFO REGISTER SGL 4-CH CMOS 16CDIP - Rail/Tube |

| CD40105BE | 功能描述:寄存器 CMOS FIFO RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時鐘頻率:36 MHz 傳播延遲時間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| CD40105BEE4 | 功能描述:寄存器 CMOS FIFO RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時鐘頻率:36 MHz 傳播延遲時間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。