- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366616 > C3ENPB0-DS 4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | C3ENPB0-DS |

| 英文描述: | 4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM |

| 中文描述: | ? - 3E的網(wǎng)絡(luò)處理器的數(shù)據(jù)資料硅修訂買0 |

| 文件頁數(shù): | 55/114頁 |

| 文件大?。?/td> | 1893K |

| 代理商: | C3ENPB0-DS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

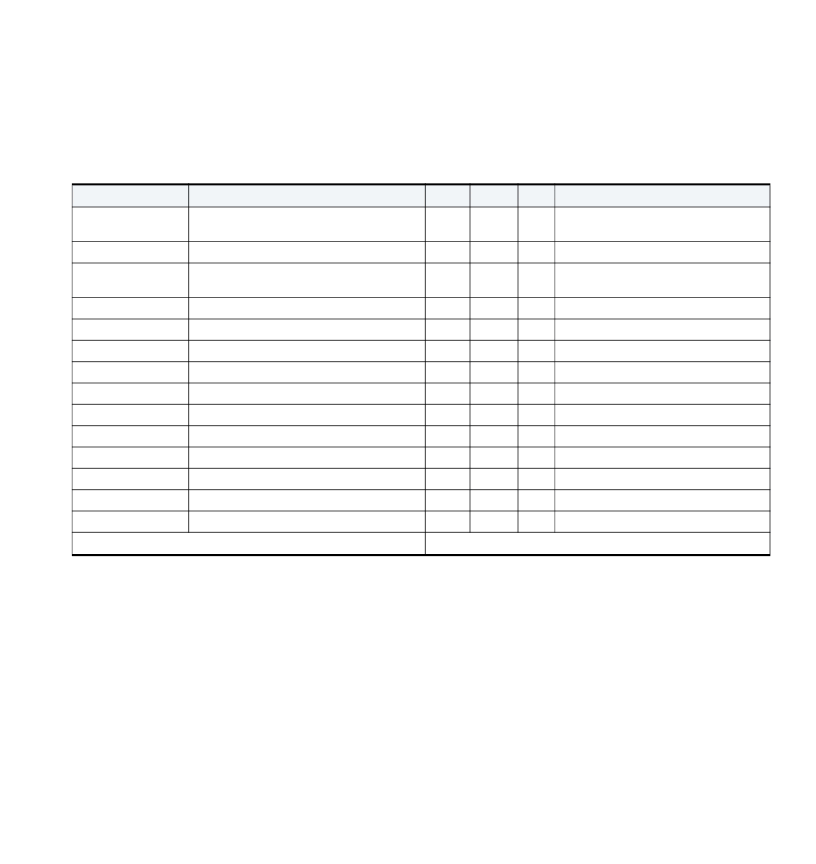

Pin Descriptions Grouped by Function

55

MOTOROLA GENERAL BUSINESS INFORMATION

C3ENPA1-DS/D REV 03

QMU to Q-5/Q-3 (External

Mode) Interface Signals

The QMU to Q-5/Q-3 signals are described in

Table 25

.

Table 25

QMU to Q-5/Q-3 (External Mode) Interface Signals

SIGNAL NAME

PIN #

TOTAL

TYPE

I/O

SIGNAL DESCRIPTION

QA0 - QA15

D10, C10, A10, F11, E11, D11, C11, B11, A11,

F12, E12, D12, C12, A12, F13, E13

16

LVTTL

O

Enqueue Data [8:23]

QA16

D13

1

LVTTL

O

Enqueue Parity

QD0 - QD23

F1, E1, D1, C1, B1, F2, E2, C2, A2, E3, D3, C3,

B3, A3, D4, B4, A4, E5, D5, C5, B5, A5, E6, C6

24

LVTTL

I

PD

Dequeue Data [0:23]

QD24 - QD31

A6, E7, D7, C7, B7, A7, E8, D8

8

LVTTL

I

PD

I

PD

I

PD

O

Enqueue Data [0:7]

QDQPAR

C8

1

LVTTL

Dequeue Parity

QARDY

F10

1

LVTTL

Dequeue Ack Ready

QNQRDY

A9

1

LVTTL

Enqueue Ready

QWEX

E10

1

LVTTL

O

Dequeue Ready

QBCLKO

B8

1

LVTTL

O

Output ClockB

QBCLKI

A8

1

LVTTL

I

PD

O

Input ClockB

QACLKO

F9

1

LVTTL

Output ClockA

QACLKI

E9

1

LVTTL

I

PD

O

Input ClockA

QDPL

C9

1

LVTTL

Dequeue Ack [0]

QDPH

B9

1

LVTTL

O

Dequeue Ack [1]

TOTAL PINS

59

F

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| C3F189AD | 4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM |

| C3GD | 5V, 64Kbit (8Kbit x 8) ZEROPOWER® SRAM |

| C5GDS | 4-BIT MAGNITUDE COMPARATOR |

| C5RDL | 8-INPUT NAND/AND GATE |

| C5RDS | CERAMIC CHIP/MIL-PRF-55681 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| C3F | 功能描述:XLR 連接器 3 PIN FEMALE RECEPT RoHS:否 制造商:Neutrik 標(biāo)準(zhǔn):Standard XLR 產(chǎn)品類型:Connectors 型式:Female 位置/觸點(diǎn)數(shù)量:3 端接類型:Solder 安裝風(fēng)格:Cable 方向:Vertical |

| C3F002KBS | 制造商:Hammond Power Solutions 功能描述:TRANSFORMER, DISTRIBUTION , ENCAPSULATED, 480V IN, 208Y/120V OUT, 2KVA |

| C3F002KDS | 制造商:Hammond Power Solutions 功能描述:POTTED N3R 3PH CU 2kVA 480-240 |

| C3F003DKS | 制造商:Hammond Power Solutions 功能描述:TRANSFORMER, N3R 3PH 3KVA 240-480Y/277 |

| C3F003KBS | 制造商:Hammond Power Solutions 功能描述:TRANSFORMER, DISTRIBUTION , ENCAPSULATED, 480V IN, 208Y/120V OUT, 3KVA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。