- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366616 > C3ENPB0-DS 4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | C3ENPB0-DS |

| 英文描述: | 4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM |

| 中文描述: | ? - 3E的網(wǎng)絡(luò)處理器的數(shù)據(jù)資料硅修訂買0 |

| 文件頁(yè)數(shù): | 52/114頁(yè) |

| 文件大小: | 1893K |

| 代理商: | C3ENPB0-DS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)當(dāng)前第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)

52

CHAPTER 2: SIGNAL DESCRIPTIONS

C3ENPA1-DS/D REV 03

MOTOROLA GENERAL BUSINESS INFORMATION

MRASX

A23

1

LVTTL

O

PD

Command Outputs: MRASX, MCASX, MWEX and

MCSX define the command being entered. MCSX

is considered part of the command code.

MWEX

A22

1

LVTTL

O

PD

Command Outputs: MRASX, MCASX, MWEX and

MCSX define the command being entered. MCSX

is considered part of the command code.

MCSX

A25

1

LVTTL

O

PD

Chip Select: MCSX enables (registered LOW) and

disables (registered HIGH) the command decoder.

All commands are masked when MCSX is

registered HIGH. MCSX provides the external bank

selection on systems with multiple banks. MCSX is

considered part of the command code.

MDQM

MDQML

A20

A21

1

1

LVTTL

LVTTL

O

PD

O

PD

Input/Output Mask: MDQM is an input mask

signal for write accesses and an output enable

signal for read accesses. Input data is masked

when MDQM is sampled HIGH during a WRITE

cycle. The output buffers are placed in a high Z

state (two-clock latency) when MDQM is sampled

HIGH during the READ cycle.

NOTE: MDQML is an identical copy of MDQM

used to drive the loading on SDRAM

configurations with 2 DQM pins.

MDCLK

A26

1

LVTTL

I

PD

Clock: MDCLK is driven by the system clock. All

SDRAM input signals are sampled on the positive

edge of the MDCLK. MDCLK also increments the

internal burst counter and controls the output

registers.

TOTAL PINS

160

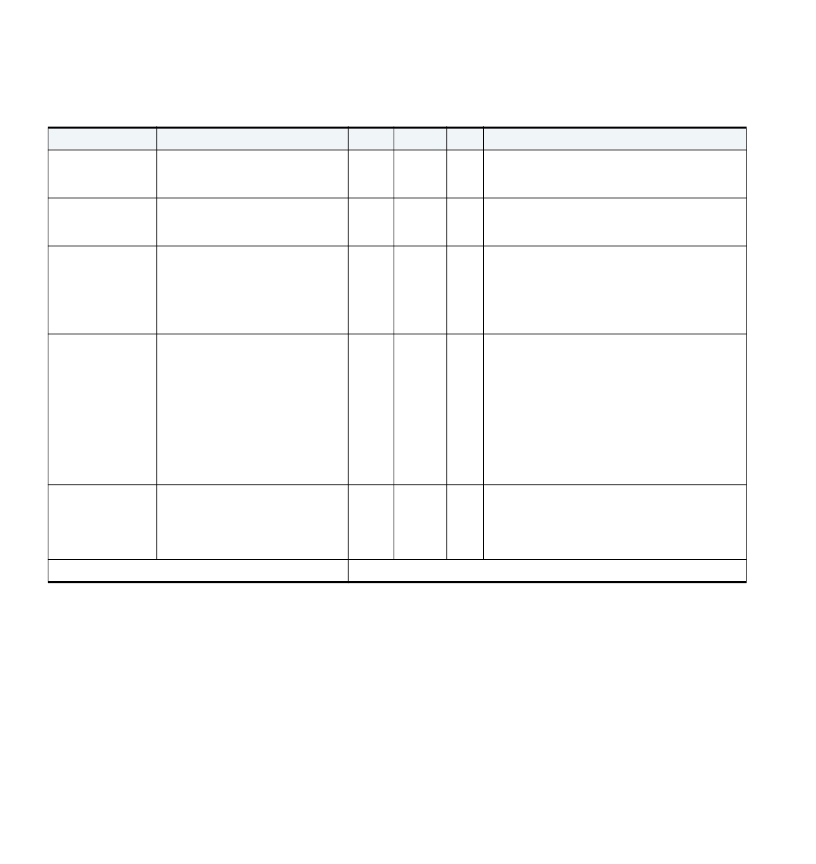

Table 22

BMU SDRAM Interface Signals (continued)

SIGNAL NAME

PIN #

TOTAL

TYPE

I/O

SIGNAL DESCRIPTION

F

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| C3F189AD | 4 Mbit (512 Kbit x 8) ZEROPOWER® SRAM |

| C3GD | 5V, 64Kbit (8Kbit x 8) ZEROPOWER® SRAM |

| C5GDS | 4-BIT MAGNITUDE COMPARATOR |

| C5RDL | 8-INPUT NAND/AND GATE |

| C5RDS | CERAMIC CHIP/MIL-PRF-55681 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| C3F | 功能描述:XLR 連接器 3 PIN FEMALE RECEPT RoHS:否 制造商:Neutrik 標(biāo)準(zhǔn):Standard XLR 產(chǎn)品類型:Connectors 型式:Female 位置/觸點(diǎn)數(shù)量:3 端接類型:Solder 安裝風(fēng)格:Cable 方向:Vertical |

| C3F002KBS | 制造商:Hammond Power Solutions 功能描述:TRANSFORMER, DISTRIBUTION , ENCAPSULATED, 480V IN, 208Y/120V OUT, 2KVA |

| C3F002KDS | 制造商:Hammond Power Solutions 功能描述:POTTED N3R 3PH CU 2kVA 480-240 |

| C3F003DKS | 制造商:Hammond Power Solutions 功能描述:TRANSFORMER, N3R 3PH 3KVA 240-480Y/277 |

| C3F003KBS | 制造商:Hammond Power Solutions 功能描述:TRANSFORMER, DISTRIBUTION , ENCAPSULATED, 480V IN, 208Y/120V OUT, 3KVA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。