- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375289 > AM29BDS640GTD9WSI (SPANSION LLC) 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory PDF資料下載

參數(shù)資料

| 型號: | AM29BDS640GTD9WSI |

| 廠商: | SPANSION LLC |

| 元件分類: | DRAM |

| 英文描述: | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| 中文描述: | 4M X 16 FLASH 1.8V PROM, 14 ns, PBGA80 |

| 封裝: | 11 X 12 MM, 0.80 MM PITCH, FBGA-80 |

| 文件頁數(shù): | 16/65頁 |

| 文件大?。?/td> | 899K |

| 代理商: | AM29BDS640GTD9WSI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

October 31, 2002

Am29BDS640G

15

A D V A N C E I N F O R M A T I O N

Low V

CC

Write Inhibit

When V

CC

is less than V

LKO

, the device does not

accept any write cycles. This protects data during V

CC

power-up and power-down. The command register and

all internal program/erase circuits are disabled, and the

device resets to reading array data. Subsequent writes

are ignored until V

CC

is greater than V

LKO

. The system

must provide the proper signals to the control inputs to

prevent unintentional writes when V

CC

is greater than

V

LKO

.

Write Pulse “Glitch” Protection

Noise pulses of less than 5 ns (typical) on OE#, CE# or

WE# do not initiate a write cycle.

Logical Inhibit

Write cycles are inhibited by holding any one of OE# =

V

IL

, CE# = V

IH

or WE# = V

IH

. To initiate a write cycle,

CE# and WE# must be a logical zero while OE# is a

logical one.

Power-Up Write Inhibit

If WE# = CE# = RESET# = V

IL

and OE# = V

IH

during

power up, the device does not accept commands on

the rising edge of WE#. The internal state machine is

automatically reset to the read mode on power-up.

V

CC

and V

IO

Power-up And Power-down

Sequencing

The device imposes no restrictions on V

CC

and V

IO

power-up or power-down sequencing. Asserting

RESET# to V

IL

is required during the entire V

CC

and

V

IO

power sequence until the respective supplies reach

their operating voltages. Once V

CC

and V

IO

attain their

respective operating voltages, de-assertion of

RESET# to V

IH

is permitted.

COMMON FLASH MEMORY INTERFACE

(CFI)

The Common Flash Interface (CFI) specification out-

lines device and host system software interrogation

handshake, which allows specific vendor-specified

software algorithms to be used for entire families of

devices. Software support can then be device-indepen-

dent, JEDEC ID-independent, and forward- and back-

ward-compatible for the specified flash device families.

Flash vendors can standardize their existing interfaces

for long-term compatibility.

This device enters the CFI Query mode when the

system writes the CFI Query command, 98h, to

address 55h any time the device is ready to read array

data. The system can read CFI information at the

addresses given in Tables 3-6. To terminate reading

CFI data, the system must write the reset command.

The system can also write the CFI query command

when the device is in the autoselect mode. The device

enters the CFI query mode, and the system can read

CFI data at the addresses given in Tables 3-6. The

system must write the reset command to return the

device to the reading array data.

For further information, please refer to the CFI Specifi-

cation and CFI Publication 100, available via the AMD

site at the following URL:

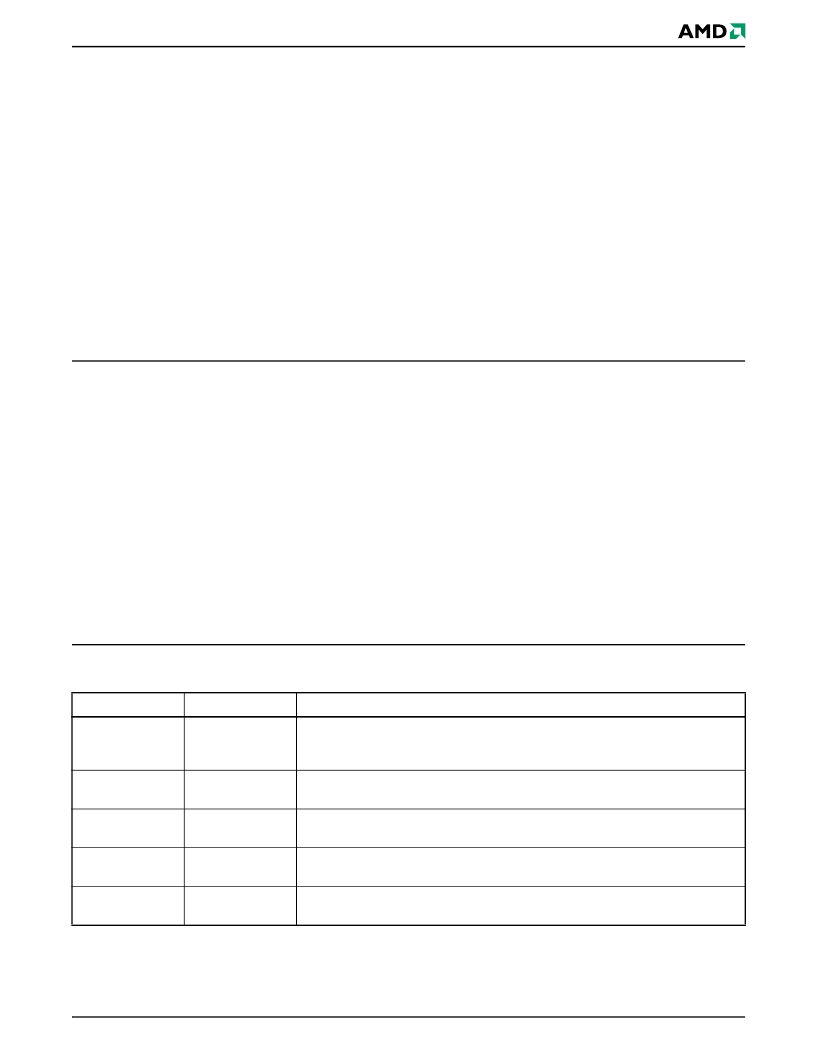

. Alternatively, contact anCFI Query Identification String

Addresses

Data

Description

10h

11h

12h

0051h

0052h

0059h

Query Unique ASCII string “QRY”

13h

14h

0002h

0000h

Primary OEM Command Set

15h

16h

0040h

0000h

Address for Primary Extended Table

17h

18h

0000h

0000h

Alternate OEM Command Set (00h = none exists)

19h

1Ah

0000h

0000h

Address for Alternate OEM Extended Table (00h = none exists)

相關PDF資料 |

PDF描述 |

|---|---|

| AM29BDS640GTD8WSI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BDS643GT7MVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BDS643GT5GVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BDS643GT5KVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

| AM29BDS643GT5MVAI | 64 Megabit (4 M x 16-Bit) CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Flash Memory |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AM29BDS643GT5KVAI | 制造商:Spansion 功能描述:FLASH PARALLEL 1.8V 64MBIT 4MX16 55NS 44FBGA - Trays |

| AM29BL802CB-65RZET | 制造商:Spansion 功能描述: |

| AM29C01WW WAF | 制造商:Advanced Micro Devices 功能描述: |

| AM29C10API | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM29C10AWW DIE | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。