- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374016 > ADMCF341 (Analog Devices, Inc.) DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End PDF資料下載

參數(shù)資料

| 型號(hào): | ADMCF341 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| 中文描述: | DashDSP⑩28引腳閃存混合信號(hào)增強(qiáng)的DSP與模擬前端 |

| 文件頁(yè)數(shù): | 22/36頁(yè) |

| 文件大小: | 1106K |

| 代理商: | ADMCF341 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

REV. 0

–22–

ADMCF341

PORTA8 is selected by bit 15 of the PORTA_SELECT

register.

The second alternate function of the PORTA4 and PORTA5

pins is selected by bit 4 of MODECTRL Register (SPORT1

mode: boot mode/UART mode).

Once PIO functionality has been selected for any or all of these

nine pins, the direction may be set by the 9-bit PORTA_DIR

register. Clearing any bit configures the corresponding PIO line

as an input, while setting the bit configures it as an output. By

default, following a reset all bits of PORTA_DIR are cleared,

configuring the PIO lines as inputs. The data of the PORTA0

to PORTA8 lines is controlled by the PORTA_DATA register.

These registers can be used to read data from those PIO lines

configured as inputs and write data to those configured as outputs.

Any of the nine pins that have been configured for PIO func-

tionality can be made to act as an interrupt source by setting

the appropriate bit of the PORTA_INTEN register. In order to

act as an interrupt source the pin must also be configured as an

input. An interrupt is generated upon a change of state (low-to-

high transition or high-to-low transition) on any input that has

been configured as an interrupt source. Following a change of

state event on any such input, the corresponding bit is set in the

PORTA_FLAG register and a common PIO interrupt is generated.

Reading the PORTA_FLAG register permits determining the

interrupt source. Reading the PORTA_FLAG register automati-

cally clears all bits of the registers. Following power-on or reset,

all bits of PORTA_INTEN are cleared so that no interrupts are

enabled.

Each PIO line has an internal pull-down resistor so that follow-

ing power-on or reset all nine lines are configured as input PIOs

and will be read as logic lows if left unconnected.

PIO Registers

The configuration of all registers of the PIO system is shown at

the end of the data sheet.

INTERRUPT CONTROL

The ADMCF341 can respond to 18 different interrupt sources

with minimal overhead. Seven of these interrupts are internal

DSP core interrupts and 11 are from the on-chip peripherals.

The seven DSP core interrupts are SPORT0 receive and

transmit, SPORT1 receive (or IRQ0) and transmit (or IRQ1),

the internal timer, and two software interrupts. The motor

control interrupts are the nine PORTA PIOs and two from the

PWM block (PWMSYNC pulse and

PWMTRIP

). All the on-chip

peripheral interrupts are multiplexed into the DSP core via the

peripheral

IRQ2

interrupt. They are also internally prioritized

and individually maskable. The start address in the interrupt

vector table for the ADMCF341 interrupt sources is shown in

Table X. The interrupts are listed from highest to lowest prior-

ity. The PWMSYNC interrupt is triggered by a low-to-high

transition on the PWMSYNC pulse. The

PWMTRIP

interrupt

is triggered on a high-to-low transition on the

PWMTRIP

pin.

A PIO interrupt is detected on any change of state (high-to-low

or low-to-high) on the PIO lines.

The entire interrupt control system of the ADMCF341 is con-

figured and controlled by the IFC, IMASK, and ICNTL

registers of the DSP core, the IRQFLAG register for the

PWMSYNC and

PWMTRIP

interrupts, and PORTA_FLAG

register for the PIO interrupts.

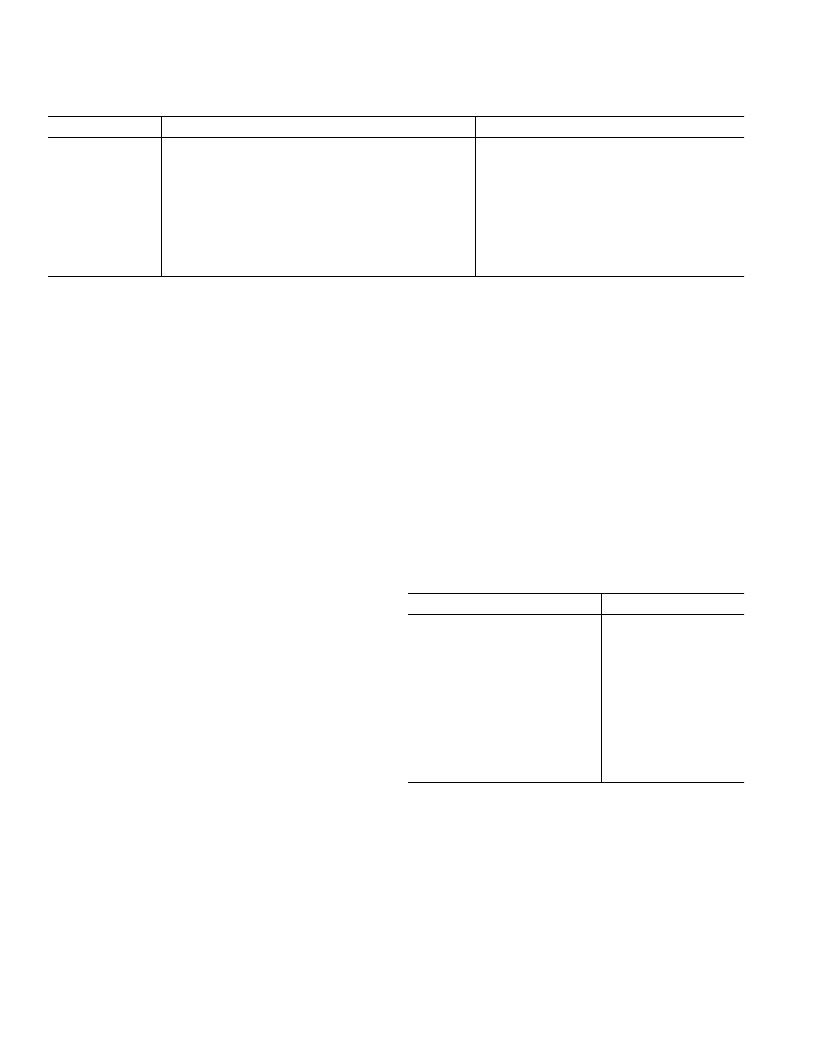

Table X. Interrupt Vector Addresses

Interrupt Source

Interrupt Vector Address

PWMTRIP

Peripheral Interrupt (

IRQ2

)

PWMSYNC

PIO

Software Interrupt 1

Software Interrupt 0

SPORT0 Transmit Interrupt

SPORT0 Receive Interrupt

SPORT1 Transmit Interrupt (or

IRQ1

) 0x0020

SPORT1 Receive Interrupt (or

IRQ0

)

Timer

0x002C (Highest Priority)

0x0004

0x000C

0x0008

0x0018

0x001C

0x0010

0x0014

0x0024

0x0028 (Lowest Priority)

Interrupt Masking

Interrupt masking (or disabling) is controlled by the IMASK

register of the DSP core. This register contains individual bits

that must be set to enable the various interrupt sources. If any

peripheral interrupt is to be enabled, the

IRQ2

interrupt enable

bit (bit 9) of the IMASK register must be set. The configuration

of the IMASK register of the ADMCF341 is shown at the end

of the data sheet.

Table IX. Port A Multiplexing

PORTA Pin

First Alternate Function (Peripheral)

Second Alternate Function (Peripheral)

PORTA8

PORTA7

PORTA6

PORTA5

PORTA4

PORTA3

PORTA2

PORTA1

PORTA0

AUX0 (Auxiliary PWM Output)

AUX1 (Auxiliary PWM Output)

DR1 (Data Receive SPORT1)

FL1 (Flag Out SPORT1)

SCLK1 (Serial Clock SPORT1)

TFS0 (Transmit Frame Sync SPORT0)

RFS0 (Receive Frame Sync SPORT0)

DT0 (Data Transmit SPORT0)

DR0 (Data Receive SPORT0)

CLKOUT (System CLOCK)

PWMSYNC (PWM)

None

DT1 (Data Transmit SPORT1)

SCLK0 (Serial Clock SPORT0)

None

None

None

None

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADMCF341BR | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341-EVALKIT | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADN2811 | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2811ACP-CML | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2811ACP-CML-RL | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADMCF341BR | 制造商:Analog Devices 功能描述:DSP Fixed-Point/Floating-Point 16-Bit 20MHz 20MIPS 28-Pin SOIC W T/R |

| ADMCF341BRZ-REEL | 制造商:Analog Devices 功能描述: |

| ADMCF341-EVALKIT | 制造商:AD 制造商全稱:Analog Devices 功能描述:DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| AD-MCX-RPSMAF | 功能描述:ADAPTER AU RPSMA FEM-MCX APPLE RoHS:是 類別:RF/IF 和 RFID >> RF配件 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

| AD-MD3FF | 制造商:Pan Pacific 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。