- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1894 > AD9952YSVZ-REEL7 (Analog Devices Inc)IC DDS DAC 14BIT 1.8V 48TQFP PDF資料下載

參數(shù)資料

| 型號: | AD9952YSVZ-REEL7 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 11/28頁 |

| 文件大小: | 0K |

| 描述: | IC DDS DAC 14BIT 1.8V 48TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 標(biāo)準(zhǔn)包裝: | 500 |

| 分辨率(位): | 14 b |

| 主 fclk: | 400MHz |

| 調(diào)節(jié)字寬(位): | 32 b |

| 電源電壓: | 1.71 V ~ 1.96 V |

| 工作溫度: | -40°C ~ 105°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-TQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 48-TQFP 裸露焊盤(7x7) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD9952

Rev. B | Page 19 of 28

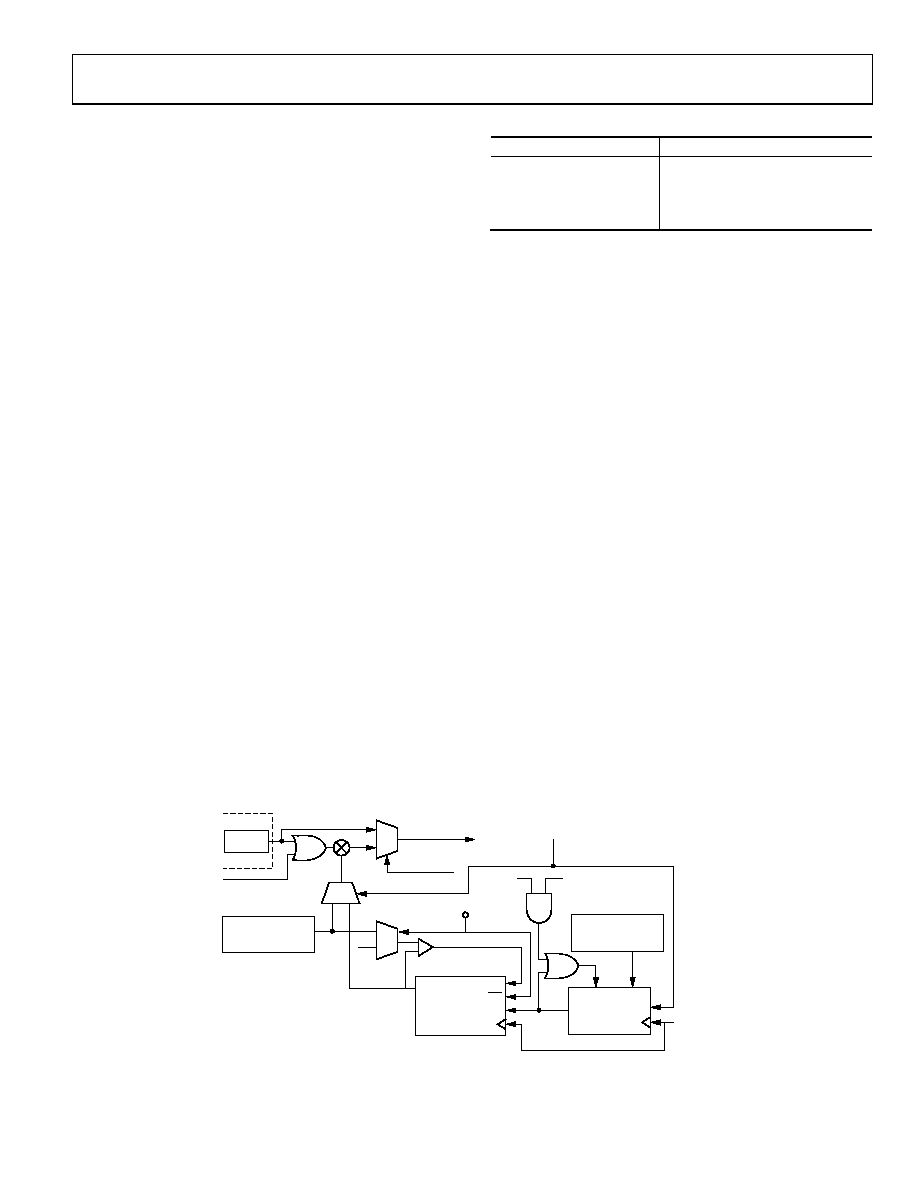

The shaped on-off keying function can be bypassed (disabled)

by clearing the OSK enable bit (CFR1 [25] = 0).

The modes are controlled by two bits located in the most

significant byte of the control function register (CFR). CFR1

[25] is the shaped on-off keying enable bit. When CFR1 [25] is

set, the output scaling function is enabled and CFR1 [25]

bypasses the function. CFR1 [24] is the internal shaped on-off

keying active bit. When CFR1 [24] is set, internal shaped on-off

keying mode is active; when CFR1 [24] is cleared, external

shaped on-off keying mode is active. CFR1 [24] is a don’t care if

the shaped on-off keying enable bit (CFR1 [25]) is cleared. The

power-up condition of the shaped on-off keying is disabled

(CFR1 [25] = 0). Figure 23 shows the block diagram of the OSK

circuitry.

Auto Shaped On-Off Keying Mode Operation

The auto shaped on-off keying mode is active when CFR1 [25]

and CFR1 [24] are set. When auto shaped on-off keying mode is

enabled, a single-scale factor is internally generated and applied

to the multiplier input for scaling the output of the DDS core

block (see Figure 23). The scale factor is the output of a 14-bit

counter that increments/decrements at a rate determined by the

contents of the 8-bit output ramp rate register. The scale factor

increases if the OSK pin is high and decreases if the OSK pin is

low. The scale factor is an unsigned value such that all 0s

multiply the DDS core output by 0 (decimal) and 0x3FFF

multiplies the DDS core output by 16,383 (decimal).

To use the full amplitude (14-bits) with fast ramp rates, the

internally generated scale factor step size is controlled via the

ASF [15:14]. Table 6 describes the increment/decrement step

size of the internally generated scale factor per the ASF [15:14].

A special feature of this mode is that the maximum output

amplitude allowed is limited by the contents of the amplitude

scale factor register. This allows the user to ramp to a value less

than full scale.

Table 6. Auto Scale Factor Internal Step Size

ASF [15:14] (Binary)

Increment/Decrement Size

00

1

01

2

10

4

11

8

OSK Ramp Rate Timer

The OSK ramp rate timer is a loadable down counter that

generates the clock signal to the 14-bit counter, which, in turn,

generates the internal scale factor. The ramp rate timer is loaded

with the value of the ASFR every time the counter reaches 1

(decimal). This load and countdown operation continues for as

long as the timer is enabled, unless the timer is forced to load

before reaching a count of 1.

If the load OSK timer bit (CFR1 [26]) is set, the ramp rate timer

is loaded upon an I/O UPDATE or upon reaching a value of 1.

The ramp timer can be loaded before reaching a count of 1 by

three methods.

The first method of loading is by changing the OSK input pin.

When the OSK input pin changes state, the ASFR value is

loaded into the ramp rate timer, which then proceeds to count

down as normal.

The second method in which the sweep ramp rate timer can be

loaded before reaching a count of 1 is if the load OSK timer bit

(CFR1 [26]) is set and an I/O UPDATE is issued.

The last method in which the sweep ramp rate timer can be

loaded before reaching a count of 1 is when going from the

inactive auto shaped on-off keying mode to the active auto

shaped on-off keying mode; that is, when the sweep enable bit is

being set.

OSK PIN

LOAD OSK TIMER

CFR1[26]

SYNC_CLK

AUTO DESK

ENABLE

CFR1[24]

TO DAC

AUTO SCALE

FACTOR GENERATOR

RAMP RATE TIMER

CLOCK

DDS CORE

OSK ENABLE

CFR[25]

AMPLITUDE SCALE

FACTOR REGISTER

(ASF)

0

1

01

HOLD

INC/DEC ENABLE

OUT

COS(X)

AMPLITUDE RAMP

RATE REGISTER

(ASF)

UP/DN

DATA

LOAD

EN

03

35

8-

0

23

Figure 23. On-Off Shaped Keying, Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9953YSVZ-REEL7 | IC DDS DAC 14BIT 1.8V 48TQFP |

| AD9954YSVZ-REEL7 | IC DDS DAC 14BIT 1.8V 48TQFP |

| AD9956YCPZ-REEL7 | IC SYNTHESIZER 1.8V 48LFCSP |

| AD9957BSVZ-REEL | IC DDS 1GSPS 14BIT IQ 100TQFP |

| AD9958BCPZ-REEL7 | IC DDS DUAL 10BIT DAC 56LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9953 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS 14-Bit, 1.8V CMOS Direct Digital Synthesizer |

| AD9953/PCB | 制造商:Analog Devices 功能描述:400 MSPS, 14BIT DGTL SYNTHESIZER - Bulk |

| AD9953ASV | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS 14-Bit, 1.8V CMOS Direct Digital Synthesizer |

| AD9953PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS 14-Bit, 1.8V CMOS Direct Digital Synthesizer |

| AD9953YSV | 制造商:Analog Devices 功能描述:Direct Digital Synthesizer 400MHz 1-DAC 14-Bit Serial 48-Pin TQFP EP 制造商:Rochester Electronics LLC 功能描述:AD9953 400 MSPS DDS W/ 14 BIT DAC - Bulk 制造商:Analog Devices 功能描述:IC DDS 400MSPS SMD 9953 TQFP48 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。