- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1980 > AD6644ASTZ-65 (Analog Devices Inc)IC ADC 14BIT 65MSPS CMOS 52-LQFP PDF資料下載

參數(shù)資料

| 型號: | AD6644ASTZ-65 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 19/24頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC ADC 14BIT 65MSPS CMOS 52-LQFP |

| 標準包裝: | 1 |

| 位數(shù): | 14 |

| 采樣率(每秒): | 65M |

| 數(shù)據(jù)接口: | 并聯(lián) |

| 轉(zhuǎn)換器數(shù)目: | 4 |

| 功率耗散(最大): | 1.3W |

| 電壓電源: | 模擬和數(shù)字 |

| 工作溫度: | -25°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 52-LQFP |

| 供應(yīng)商設(shè)備封裝: | 52-LQFP(10x10) |

| 包裝: | 托盤 |

| 輸入數(shù)目和類型: | 1 個差分,雙極 |

AD6644

Rev. D | Page 4 of 24

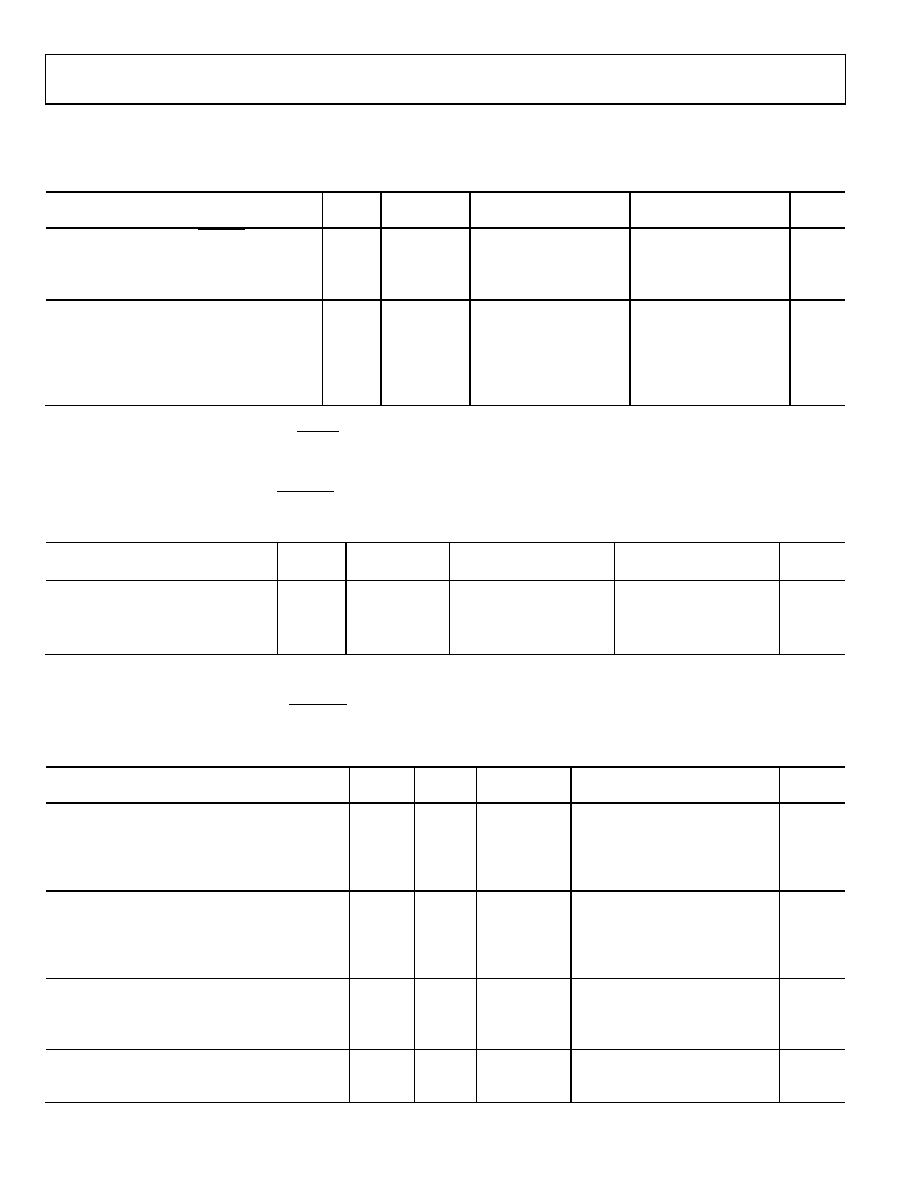

DIGITAL SPECIFICATIONS

AVCC = 5 V, DVCC = 3.3 V; TMIN = 25°C, TMAX = +85°C, unless otherwise noted.

Table 2.

AD6644AST-40

AD6644AST-65

Parameter

Temp

Test Level1

Min

Typ

Max

Min

Typ

Max

Unit

ENCODE INPUTS (ENCODE, ENCODE)

Differential Input Voltage2

Full

IV

0.4

V p-p

Differential Input Resistance

25°C

V

10

kΩ

Differential Input Capacitance

25°C

V

2.5

pF

LOGIC OUTPUTS (D13 to D0, DRY, OVR)

Logic Compatibility

CMOS

Logic 1 Voltage3

Full

V

2.5

V

Logic 0 Voltage3

Full

V

0.4

V

Output Coding

Twos complement

DMID

Full

V

DVCC/2

V

1 See the Explanation of Test Levels section.

2 All ac specifications tested by driving ENCODE and ENCODE differentially. Reference Figure 18 for performance vs. encode power.

3 Digital output logic levels: DVCC = 3.3 V, CLOAD = 10 pF. Capacitive loads >10 pF degrade performance.

SWITCHING SPECIFICATIONS

AVCC = 5 V, DVCC = 3.3 V; ENCODE and ENCODE = maximum conversion rate MSPS; TMIN = –25°C, TMAX = +85°C, unless otherwise noted.

Table 3.

AD6644AST-40

AD6644AST-65

Parameter

Temp

Test Level1

Min

Typ

Max

Min

Typ

Max

Unit

Maximum Conversion Rate

Full

II

40

65

MSPS

Minimum Conversion Rate

Full

IV

15

MSPS

ENCODE Pulse Width High

Full

IV

10

6.5

ns

ENCODE Pulse Width Low

Full

IV

10

6.5

ns

1 See the Explanation of Test Levels section.

AVCC = 5 V, DVCC = 3.3 V; ENCODE and ENCODE = maximum conversion rate MSPS; TMIN = 25°C, TMAX = +85°C, CLOAD = 10 Pf,

unless otherwise noted.

Table 4.

AD6644AST-40/65

Parameter

Name

Temp

Test Level1

Min

Typ

Max

Unit

ENCODE INPUT PARAMETERS2

Encode Period @ 65 MSPS

tENC

Full

V

15.4

ns

Encode Period @ 40 MSPS

tENC

Full

V

25

ns

Encode Pulse Width High3 @ 65 MSPS

tENCH

Full

IV

6.2

7.7

9.2

ns

Encode Pulse Width Low @ 65 MSPS

tENCL

Full

IV

6.2

7.7

9.2

ns

ENCODE/DATA READY

Encode Rising to Data Ready Falling

tDR

Full

IV

2.6

3.4

4.6

ns

Encode Rising to Data Ready Rising

tE_DR

tENCH + tDR

@ 65 MSPS (50% Duty Cycle)

Full

IV

10.3

11.1

12.3

ns

@ 40 MSPS (50% Duty Cycle)

Full

IV

15.1

15.9

17.1

ns

ENCODE/DATA (D13:0), OVR

ENCODE to DATA Falling Low

tE_FL

Full

IV

3.8

5.5

9.2

ns

ENCODE to DATA Rising Low

tE_RL

Full

IV

3.0

4.3

6.4

ns

ENCODE to DATA Delay (Hold Time)4

tH_E

Full

IV

3.0

4.3

6.4

ns

ENCODE to DATA Delay (Setup Time)5

tS_E

tENC tE_FL

Encode = 65 MSPS (50% Duty Cycle)

Full

IV

6.2

9.8

11.6

ns

Encode = 40 MSPS (50% Duty Cycle)

Full

IV

15.9

19.4

21.2

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6645ASVZ-105 | IC ADC 14BIT 105MSPS 52TQFP |

| AD6654BBC | IC ADC 14BIT W/6CH RSP 256CSPBGA |

| AD670KNZ | IC ADC 8BIT SGNL COND 20DIP |

| AD673JNZ | IC ADC 8BIT REF/CLK/COMP 20DIP |

| AD674BJN | IC ADC 12BIT MONO 3OUT 28-DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6644ASTZ-65 | 制造商:Analog Devices 功能描述:A/D Converter (A-D) IC |

| AD6644PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 40 MSPS/65 MSPS A/D Converter |

| AD6644ST | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 40 MSPS/65 MSPS A/D Converter |

| AD6644ST/PCB | 制造商:Analog Devices 功能描述:EVALUATION BOARD ((NW)) |

| AD6644ST/PCBZ | 制造商:Analog Devices 功能描述:14-BIT, 40 MSPS/65 MSPS A/D CONVERTER 制造商:Analog Devices 功能描述:AD6644 EVALUATION BOARD - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。