- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375230 > AD1821 (Analog Devices, Inc.) MODIO(Modem over Audio) SoundComm Host Signal Processing Codec(音頻調制SoundComm型主信號處理編解碼器) PDF資料下載

參數(shù)資料

| 型號: | AD1821 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | Codec |

| 英文描述: | MODIO(Modem over Audio) SoundComm Host Signal Processing Codec(音頻調制SoundComm型主信號處理編解碼器) |

| 中文描述: | MODIO(調制解調器多音頻)SoundComm主機信號處理編解碼器(音頻調制SoundComm型主信號處理編解碼器) |

| 文件頁數(shù): | 30/44頁 |

| 文件大?。?/td> | 284K |

| 代理商: | AD1821 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD1821

–30–

REV. 0

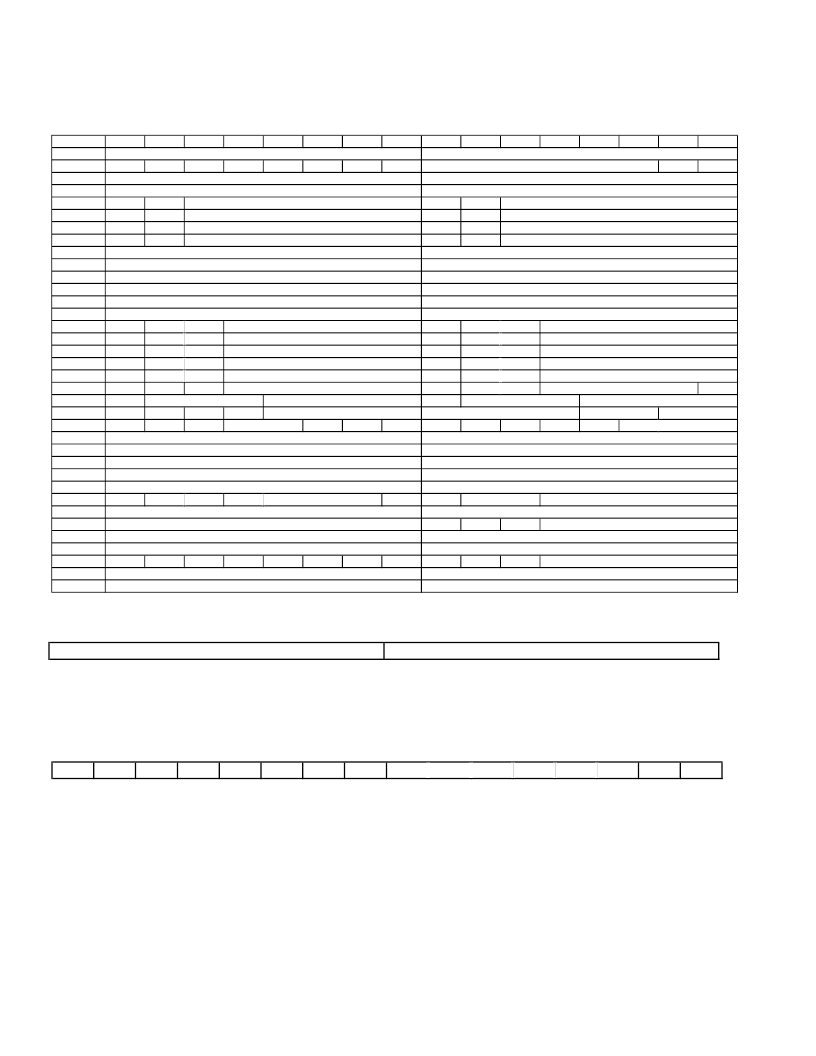

T able VIII. Sound System Indirect Registers

(High Byte)

5

(Low Byte)

4

LBT D [7:0]

ADDRESS

00 (0x00)

01 (0x01)

02 (0x02)

03 (0x03)

04 (0x04)

05 (0x05)

06 (0x06)

07 (0x07)

08 (0x08)

09 (0x09)

10 (0x0A)

11 (0x0B)

12 (0x0C)

13 (0x0D)

14 (0x0E)

15 (0x0F)

16 (0x10)

17 (0x11)

18 (0x12)

19 (0x13)

20 (0x14)

32 (0x20)

33 (0x21)

34 (0x22)

35 (0x23)

36 (0x24)

37 (0x25)

38 (0x26)

39 (0x27)

40 (0x28)

41 (0x29 )

42 (0x2A)

43 (0x2B)

44 (0x2C)

45 (0x2D)

46 (0x2E)

7

6

4

3

2

1

0

7

6

5

3

2

1

0

RES

PIE

CIE

T IE

VIE

VPSR [15.8]

VCSR [15:8]

DIE

RIE

JIE

SIE

RES

X C1

X C0

VPSR [7:0]

VCSR [7:0]

LVM

LFMM

LS1M

LS0M

RES

RES

RES

RES

LVA [5:0]

LFMA [5:0]

LS1A [5:0]

LS0A [5:0]

RVM

RFMM

RS1M

RS0M

RES

RES

RES

RES

RVA [5:0]

RFMA [5:0]

RS1A [5:0]

RS0A [5:0]

PBC [15:8]

PCC [15:8]

CBC [15:8]

CCC [15:8]

T BC [15:8]

T CC [15:8]

PBC [7:0]

PCC [7:0]

CBC [7:0]

CCC [7:0]

T BC [7:0]

T CC [7:0]

LMVM

LCDM

LSYM

LVDM

LLM

MCM

LAGC

WSE

DS1

RES

RES

RES

RES

RES

LMVA [4:0]

LCDA [4:0]

LSYA [4:0]

LVDA [4:0]

LLA [4:0]

MCA [4:0]

RMVM

RCDM

RSYM

RVDM

RLM

PIM

RAGC

RES

RES

RES

RES

RES

RES

RMVA [4:0]

RCDA [4:0]

RSYA [4:0]

RVDA [4:0]

RLA [4:0]

PIA [3:0]

M20

RES

RES

LAS [2:0]

RES

DIT

LAG [3:0]

RES

ADR

RAS [2:0]

RAG [3:0]

CDE

DS0

C NP

COF [3:0]

PBI

I2SF1 [1:0]

I01

I2SF0 [1:0]

DFS [2:0]

RES

I1T

I0T

C PI

FMI

I1I

FMSR [7:0]

S1SR [7:0]

S0SR [7:0]

RES

PCR [7:0]

FSMR [15:8]

S1SR [15:8]

S0SR [15:8]

RES

PCR [15:8]

3DDM

RES

3DD [3:0]

RES

POM

RES

POA [4:0]

RES

RES

RES

VMU

VUP

VDN

BM [4:0]

MB0R [15:8]

MB1R [15:8]

PIR

VER [15:8]

RES

MB0R [7:0]

MB1R [7:0]

C PD

RES

PIW

PAA

PDA

PD P

PT B

3D

PD3D

GPSP

RES

VER [7:0]

RES

[00] INDIRE C T LOW BY T E T MP

7

6

5

DE F AUL T = [0xX X ]

2

1

4

3

2

1

0

7

6

5

4

3

0

RES

LBT D [7:0]

LBT D [7:0] Low Byte T emporary Data holding latch for register pair writes;

Written on any write to [SSBase + 2],

Read from [SSBase + 2] when the indirect address is 0x00.

[01] INT E RRUPT E NABL E AND E X T E RNAL C ONT ROL

7

6

5

4

PIE

C IE

T IE

VIE

DE F AUL T = [0x0102]

2

1

X C1

3

2

1

0

7

6

5

4

3

0

DIE

RIE

JIE

SIE

RES

X C0

X C0

RW

External Control 0. T he state of this bit is reflected on the X CT L0 pin. T his pin is also muxed with

PCLK O. COF must be greater than 11 for PCLK O to be disabled, see SS [32].

External Control 1. T he state of this bit is reflected on the X CT L1 pin. X CT L1 may also be used for

Ring-In Interrupt.

SoundBlaster Interrupt Enable;

0

SoundBlaster Interrupt disabled

1

SoundBlaster Interrupt enabled

Joystick Interrupt Enable;

0

Joystick Interrupt disabled

1

Joystick Interrupt enabled

X C1

RW

SIE

RW

JIE

RW

相關PDF資料 |

PDF描述 |

|---|---|

| AD1839A | 2 ADC, 6 DAC, 96 kHz, 24-Bit Sigma-Delta Codec |

| AD1839AAS | 2 ADC, 6 DAC, 96 kHz, 24-Bit Sigma-Delta Codec |

| AD1839AAS-REEL | 2 ADC, 6 DAC, 96 kHz, 24-Bit Sigma-Delta Codec |

| AD1839AASZ-REEL1 | 2 ADC, 6 DAC, 96 kHz, 24-Bit Sigma-Delta Codec |

| AD1839AASZ1 | 2 ADC, 6 DAC, 96 kHz, 24-Bit Sigma-Delta Codec |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD1821JS | 制造商:Analog Devices 功能描述: |

| AD1821JS-M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Soundcard Circuits |

| AD-1825 | 制造商:UNBRANDED 功能描述:ADAPTOR 18V 250MA |

| AD-1825 | 制造商:UNBRANDED 功能描述:ADAPTOR 18V 250MA |

| AD1826-0013 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。