- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25515 > 952601YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 952601YGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件頁數(shù): | 11/25頁 |

| 文件大小: | 227K |

| 代理商: | 952601YGLFT |

IDTTM

Progammable Timing Control HubTM for Next Gen P4TM Processor

701J—01/25/10

ICS952601

Programmable Timing Control HubTM for Next Gen P4TM Processor

19

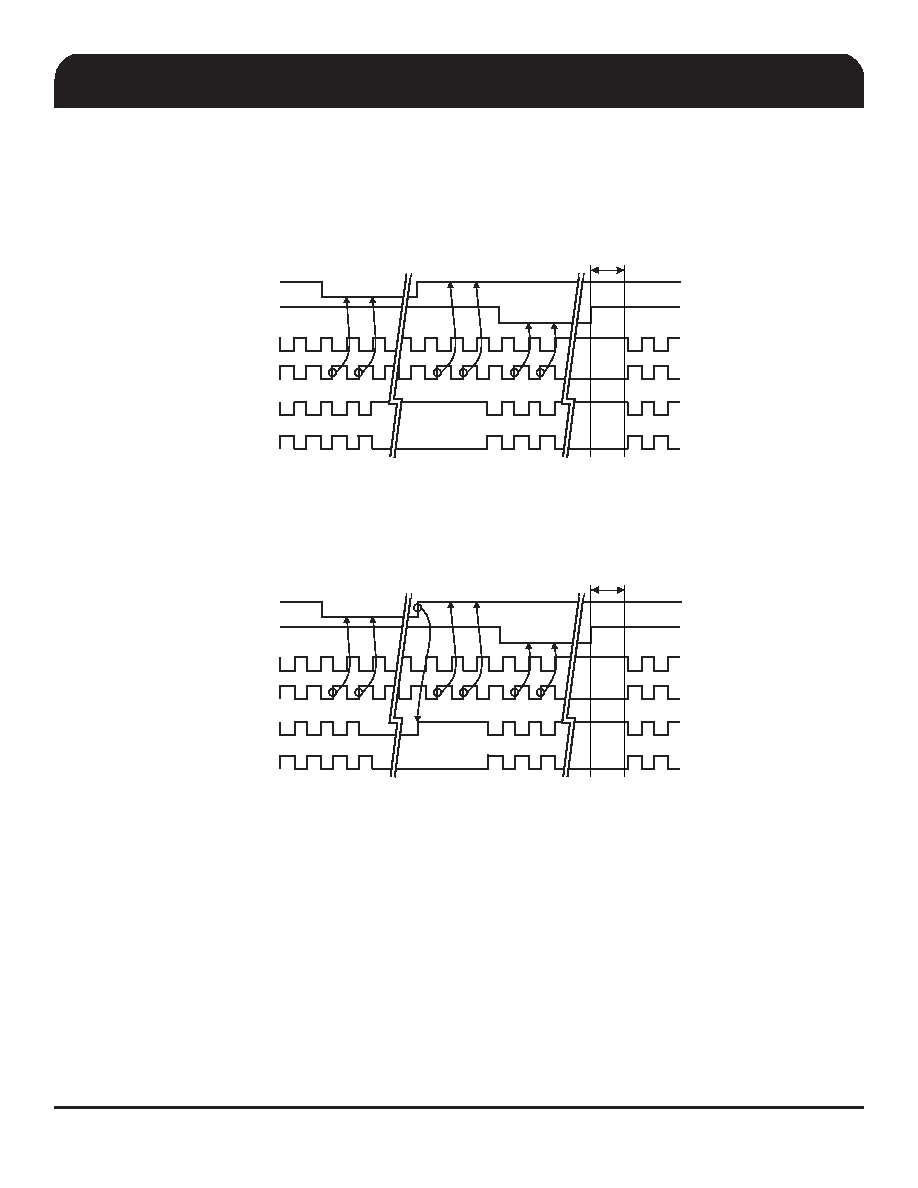

The following diagrams illustrate CPU clock timing during CPU_Stop# and PwrDwn# modes with CPU_PwrDwn and

CPU_Stop tristate control bits set to driven or tristate in byte 2 of the control register.

CPU_Stop = Driven, CPU_Pwrdwn = Driven

CPU_Stop#

1.8mS

PD#

CPU (Free Running)

CPU# (Free Running)

CPU (Stoppable)

CPU# (Stoppable)

Notes:

1. When both bits (CPU_Stop & CPU_Pwrdown tristate bits) are low, the clock chip will never tristate CPU output clocks

(assuming clock's OE bit is set to "1")

CPU Clock Tristate Timing

CPU_Stop = Tristate, CPU_Pwrdwn = Driven

CPU_Stop#

1.8mS

PD#

CPU (Free Running)

CPU# (Free Running)

CPU (Stoppable)

CPU# (Stoppable)

Notes:

1. Tristate outputs are pulled low by output termination resistors as shown here.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 952601YFLFT | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952703BF | 217.9 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952801CFLFT | 293.34 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952807 | MODULAR TERMINAL BLOCK |

| 9528090000 | 10 A, MODULAR TERMINAL BLOCK, 1 DECK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 952606PFLF | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Synthesizer Dual 48-Pin SSOP Tube |

| 9526-1000-60 | 制造商:Belden Inc 功能描述:Shielded Paired Cable Number of Conducto |

| 952618BFLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF GENERAL PURPOSE SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF General Purpose Semiconductors |

| 952620CFLF | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

| 952620CFLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。