- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25515 > 952302AGT (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | 952302AGT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-48 |

| 文件頁數(shù): | 6/17頁 |

| 文件大小: | 153K |

| 代理商: | 952302AGT |

14

ICS952302

0957B—10/05/04

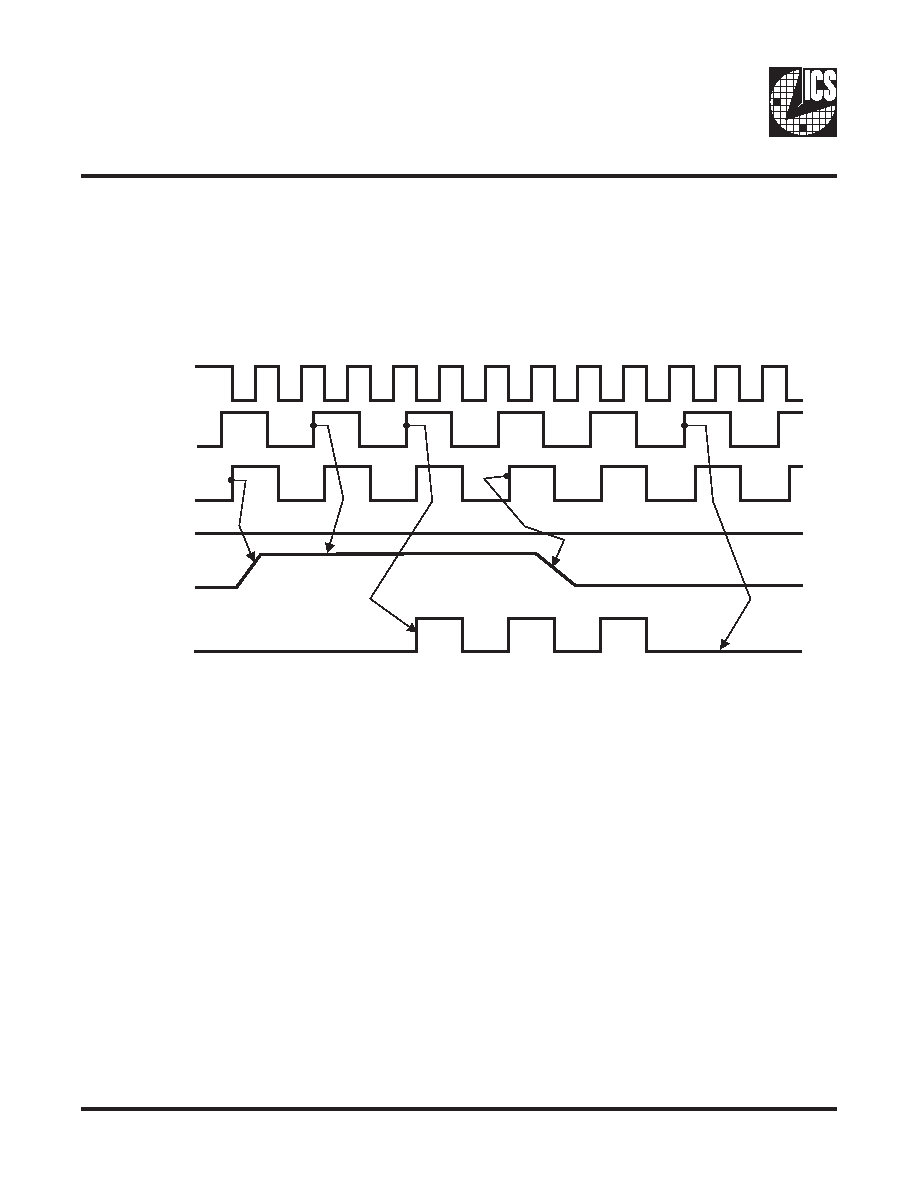

PCI_STOP# Timing Diagram

PCI_STOP# is an asynchronous input to the ICS952302. It is used to turn off the PCICLK clocks for low power operation.

PCI_STOP# is synchronized by the ICS952302 internally. The minimum that the PCICLK clocks are enabled

(PCI_STOP# high pulse) is at least 10 PCICLK clocks. PCICLK clocks are stopped in a low state and started with a

full high pulse width guaranteed. PCICLK clock on latency cycles are only three rising PCICLK clocks, off latency is

one PCICLK clock.

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS952302 device.)

2. PCI_STOP# is an asynchronous input, and metastable conditions may exist. This signal is required to be synchronized

inside the ICS952302.

3. All other clocks continue to run undisturbed.

4. CLK_STOP# is shown in a high (true) state.

CPUCLK

(Internal)

PCICLK_F

(Internal)

PCICLK_F

(Free-running)

CLK_STOP#

PCICLK

PCI_STOP#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 95231DC | 95K SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16 |

| 952601EGLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952601EFLF | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952601EFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952601YGLFT | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 952303 | 制造商:Weidmuller 功能描述:NEXT 26/26/16 3GP PAINTED -EA - Bulk |

| 9523030000 | 制造商:Weidmuller 功能描述:NEXT 26/26/16 3GP PAINTED |

| 952304 | 制造商:Weidmuller 功能描述:NEXT 38/26/16 3GP PAINTED -EA - Bulk |

| 9523040000 | 制造商:Weidmuller 功能描述:NEXT 38/26/16 3GP PAINTED |

| 9523042 | 制造商:Molex 功能描述:CONNECTOR PCB 4WAY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。