- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36337 > 935261504557 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | 935261504557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封裝: | PLASTIC, SOT-307, QFP-44 |

| 文件頁(yè)數(shù): | 20/87頁(yè) |

| 文件大小: | 440K |

| 代理商: | 935261504557 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)

1999 Jul 01

27

Philips Semiconductors

Product specication

9-bit video input processor

SAA7113H

Some details about data types:

Active video (data type 15) component YUV4:2:2

signal, 720 active pixels per line. Format and nominal

levels are given in Fig.23 and Table 13.

Test line (data type 6), is similar to decoded YUV-data

as in active video, with two exceptions:

– vertical filter (chrominance comb filter for NTSC

standards, PAL-phase-error correction) within the

chrominance processing is disabled

– peaking and chrominance trap are bypassed within

the luminance processing, if I2C-bus bit VBLB is set.

This data type is defined for future enhancements; it

could be activated for lines containing standard test

signals within the vertical blanking period; currently

the most sources do not contain test lines.

This data type is available only in lines with VREF = 0,

see I2C-bus detail section, Table 45.

Format and nominal levels are given in Fig.23 and

Table 13.

Raw samples (data type 7) oversampled CVBS-signal

for intercast applications; the data rate is 27 MHz.

The horizontal range is programmable via

HSB7 to HSB0, HSS7 to HSS0 and HDEL1 to HDEL0;

see I2C-bus section subaddresses 06H, 07H and 10H

and Tables 33, 34 and 46.

Format and nominal levels are given in Fig.24 and

Table 15.

Sliced data (various standards, data types 0 to 5 and

8 to 14).

The format is given in Table 17.

The data type selections by LCR are overruled by setting

VIPB (subaddress 11H bit 1) to logic 1. This setting is

mainly intended for device production tests. The VPO-bus

carries the upper or lower 8 bits of the two ADCs

depending on the ADLSB (subaddress 13H bit 7) setting.

The output configuration is done via MODE3 to MODE0

settings (subaddress 02H bits 3 to 0, see Table 27). If the

YC-mode is selected, the VPO-bus carries the multiplexed

output signals of both ADCs, in CVBS-mode the output of

only one ADC. No timing reference codes are generated in

this mode.

Note: The LSBs (bit 0) of the ADCs are available on

pins RTS0 or RTS1. See Chapter 15, subaddress 12H for

details.

The SAV/EAV timing reference codes define start and end

of valid data regions.

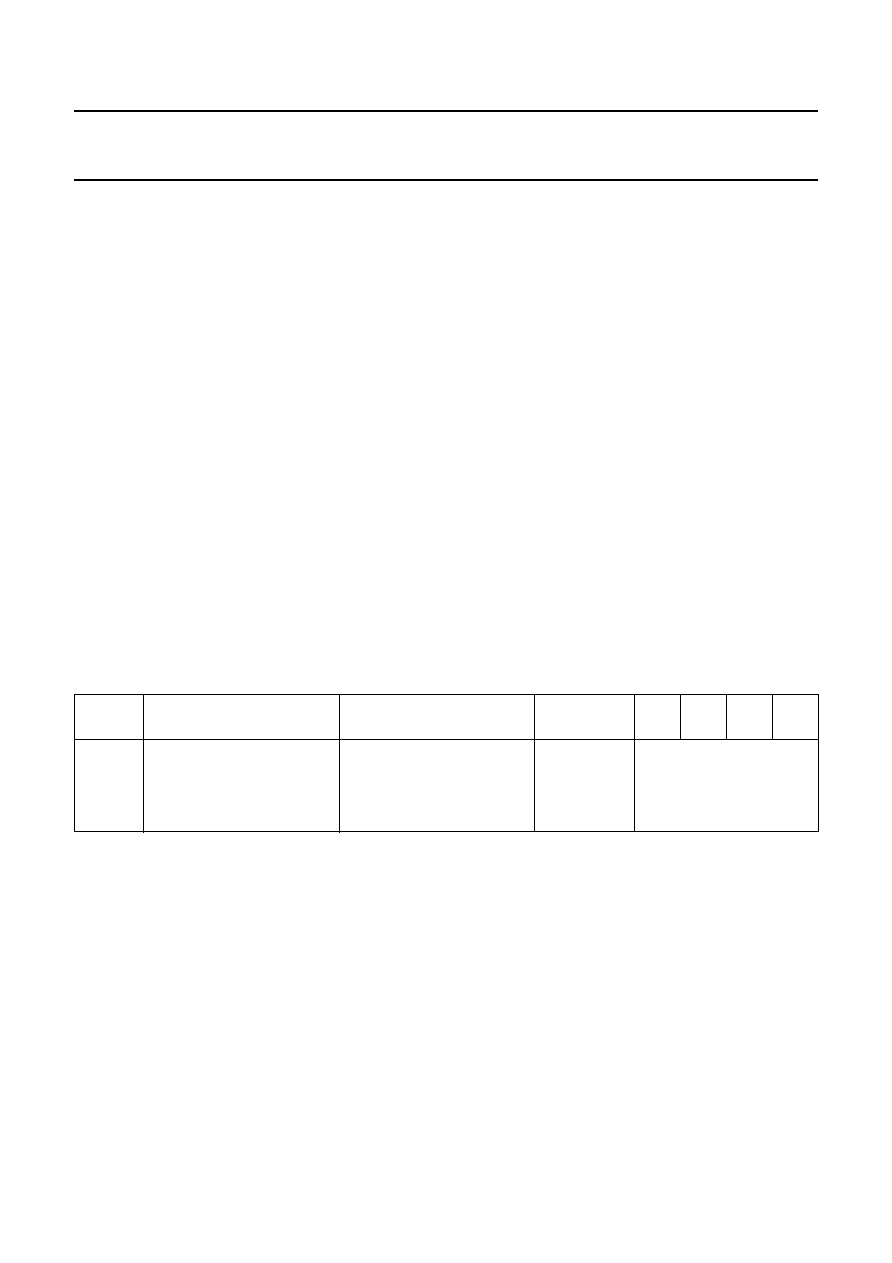

Table 5

SAV/EAV format

BIT 7

BIT 6 (F)

BIT 5 (V)

BIT 4 (H)

BIT 3

(P3)

BIT 2

(P2)

BIT 1

(P1)

BIT 0

(P0)

1

eld bit

1st eld: F = 0;

2nd eld: F = 1;

for vertical timing

see Tables 6 and 7

vertical blanking bit

VBI: V = 1;

active video: V = 0;

for vertical timing

see Tables 6 and 7

H = 0 in SAV;

H = 1 in EAV

reserved; evaluation not

recommended (protection

bits according to ITU 656)

The generation of the H-bit and consequently the timing of

SAV/EAV corresponds to the selected data format. H = 0

during active data region. For all data formats excluding

data type 7 (raw data), the length of the active data region

is 1440 LLC. For the YUV 4:2:2 formats (data

types 15 and 6) every clock cycle within this range

contains valid data, see Table 13.

The sliced data stream (various standards, data types

0 to 5 and 8 to 14; see Table 17) contains also invalid

cycles marked as 00H.

The length of the raw data region (data type 7) is

programmable via HSB7 to HSB0 and HSS7 to HSS0

(subaddresses 06H and 07H; see Fig.24).

During horizontal blanking period between EAV and SAV

the ITU-blanking code sequence ‘-80-10-80-10-...’ is

transmitted.

The position of the F-bit is constant according to ITU 656

(see Tables 6 and 7).

The V-bit can be generated in four different ways

(see Tables 6 and 7) controlled via OFTS1 and OFTS0

(subaddress 10H, bits 7 and 6), VRLN (subaddress 10H,

bit 3) and LCR2 to LCR24 (subaddresses 41H to 57H).

F and V bits change synchronously with the EAV code.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935261537118 | DELTA-SIGMA ADC, PDSO16 |

| 935261537112 | DELTA-SIGMA ADC, PDSO16 |

| 935261615112 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935261615118 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935261616112 | SPECIALTY CONSUMER CIRCUIT, PDIP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。