- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36335 > 935247890551 (NXP SEMICONDUCTORS) PICTURE-IN-PICTURE IC, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | 935247890551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 畫面疊加 |

| 英文描述: | PICTURE-IN-PICTURE IC, PQFP100 |

| 封裝: | PLASTIC, SOT-317-2, QFP-100 |

| 文件頁數(shù): | 35/35頁 |

| 文件大小: | 228K |

| 代理商: | 935247890551 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁

1996 Aug 07

9

Philips Semiconductors

Preliminary specication

Picture-In-Picture (PIP) controller

SAB9077H

FUNCTIONAL DESCRIPTION

Pixel rate

The internal chrominance format used is 4 : 1 : 1. It is

expected that the bandwidth of the input signals is limited

to 4.5 MHz for the Y input and 1.125 MHz for the U/V

inputs.

The Y input is sampled with a 1728

× Hsync (≈27.0 MHz)

clock and is filtered and down sampled to the internal

864

× Hsync (≈13.5 MHz) pixel rate.

The U and V inputs are multiplexed and sampled with a

432

× Hsync clock and down sampled to the internal

216

× Hsync (≈3.375 MHz) pixel rate.

Acquisition area

Synchronization is done via the acquisition HSync and

VSync pins. With the acquisition fine positioning added to a

system constant the starting point of the acquisition can be

controlled.

The acquisition area is 672 pixels/line and 228 lines/field

for NTSC and 276 lines/field for PAL. Both main and

sub-channel are equivalent in handling the data.

Display mode

The internal display pixel rate is 864

× DPHsync which is

13.5 MHz. This pixel rate is upsampled by interpolation to

1728

× DPHsync before the DAC stage.

Display area

The display background is an area of 696 pixels for both

PAL and NTSC, 238 lines for NTSC and 286 lines for PAL.

This can be put on/off by the BGON bit independent of the

PIPON bits. This area can be moved by the display

background fine positioning (BGHFP and BGVFP).

Its colour is determined by the BGCOL and BGBRT bits.

Within this area PIPs are defined dependent on the

PIP mode. The PIP sizes are determined by the display

reduction factors as is shown in Table 2. Whether a PAL or

NTSC fixed number is used is depends on the DPAL bit.

The display fine positioning determines the location of the

PIPs with respect to the background. sub and

main-channel both have their independent PIP size and

location control, which is shown in Fig.3.

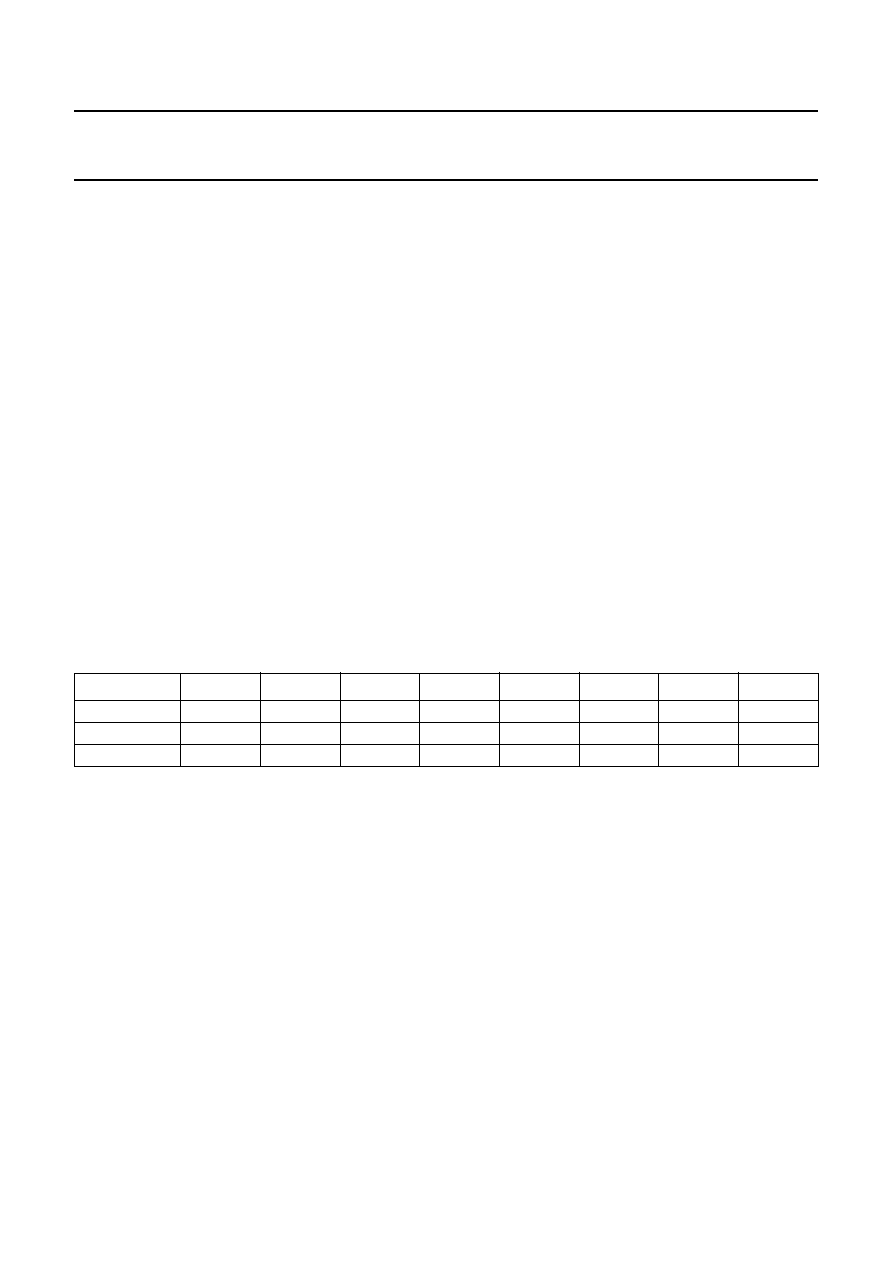

Table 2

PIP sizes

REDUCTION

H/1

H/2

H/3

H/4

V/1

V/2

V/3

V/4

Pixels

672

336

224

168

NTSC-lines

228

114

76

57

PAL-lines

276

138

92

69

相關PDF資料 |

PDF描述 |

|---|---|

| 935247890557 | PICTURE-IN-PICTURE IC, PQFP100 |

| 935249180112 | 12 W, 4 CHANNEL, AUDIO AMPLIFIER, PZIP17 |

| 935251700112 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935251700118 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935251700512 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

| 935252-5 | 制造商:C-H 功能描述:935252-5 |

| 935257650112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY ICSUBS TO 935257650112 |

| 935260093112 | 制造商:NXP Semiconductors 功能描述:IC AVIC ADV BASESTATION 14SOIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。