- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24793 > 935246150005 (NXP SEMICONDUCTORS) 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, UUC PDF資料下載

參數(shù)資料

| 型號: | 935246150005 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, UUC |

| 封裝: | CHIP ON WAFER |

| 文件頁數(shù): | 39/68頁 |

| 文件大小: | 234K |

| 代理商: | 935246150005 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

2000 Jan 04

44

Philips Semiconductors

Product specication

Stand-alone CAN controller

SJA1000

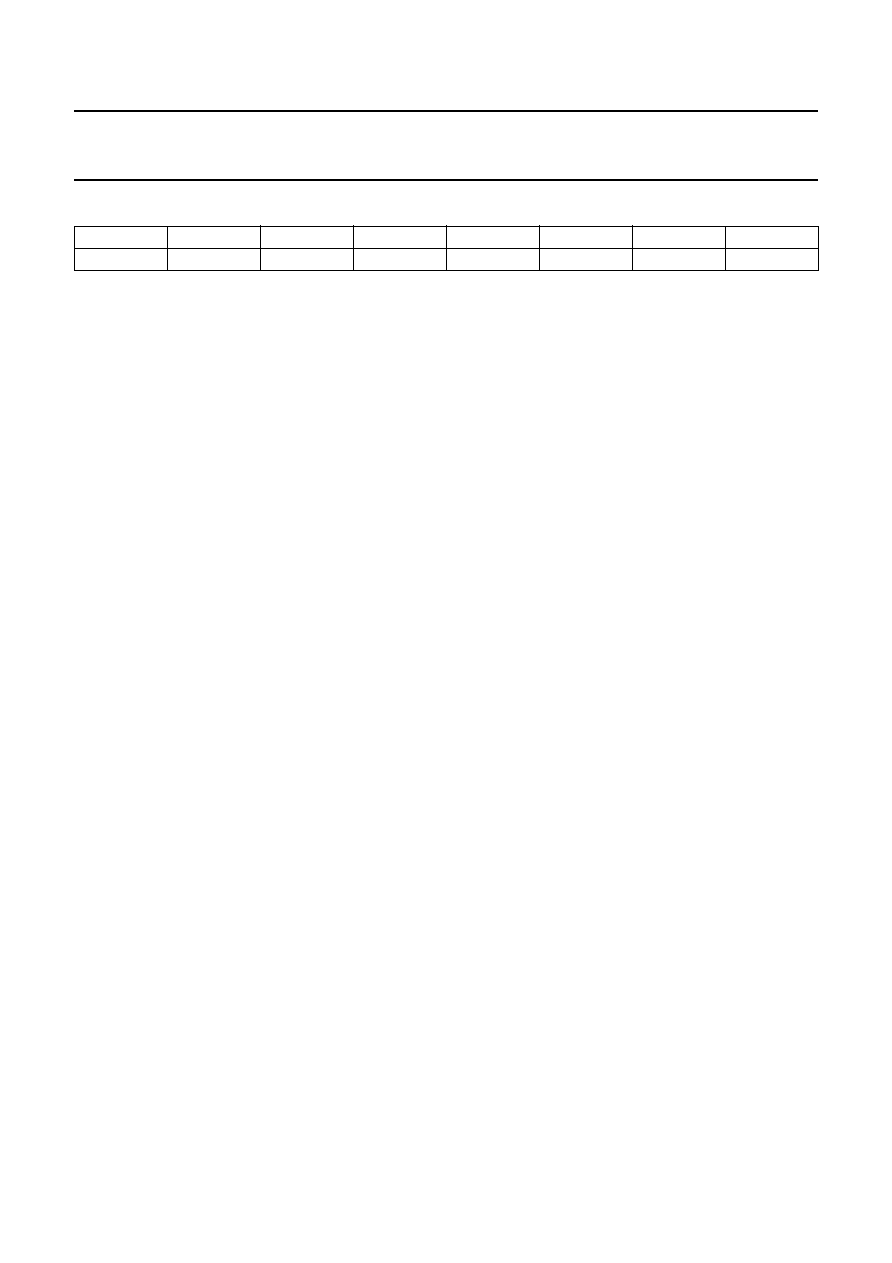

Table 41 RX identier 4 (EFF); can address 20; note 1

Notes

1. ID.X means identifier bit X.

2. Remote transmission request.

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

ID.4

ID.3

ID.2

ID.1

ID.0

RTR(2)

00

Remark: the received data length code located in the

frame information byte represents the real sent data length

code, which may be greater than 8 (depends on sender).

Nevertheless the maximum number of received data bytes

is 8. This should be taken into account by reading a

message from the receive buffer.

As described in Fig.8 the RXFIFO has space for

64 message bytes in total. It depends on the data length

how many messages can fit in it at one time. If there is not

enough space for a new message within the RXFIFO, the

CAN controller generates a data overrun condition the

moment this message becomes valid and the acceptance

test was positive. A message which is partly written into

the RXFIFO, when the data overrun situation occurs, is

deleted. This situation is indicated to the CPU via the

status register and the data overrun interrupt, if enabled.

6.4.15

ACCEPTANCE FILTER

With the help of the acceptance filter the CAN controller is

able to allow passing of received messages to the RXFIFO

only when the identifier bits of the received message are

equal to the predefined ones within the acceptance filter

registers.

The acceptance filter is defined by the Acceptance Code

Registers (ACRn) and the Acceptance Mask Registers

(AMRn). The bit patterns of messages to be received are

defined within the acceptance code registers.

The corresponding acceptance mask registers allow to

define certain bit positions to be ‘don’t care’.

Two different filter modes are selectable within the mode

register (MOD.3, AFM; see Section 6.4.3):

Single filter mode (bit AFM is logic 1)

Dual filter mode (bit AFM is logic 0).

6.4.15.1

Single lter conguration

In this filter configuration one long filter (4-bytes) could be

defined. The bit correspondences between the filter bytes

and the message bytes depend on the currently received

frame format.

Standard frame: if a standard frame format message is

received, the complete identifier including the RTR bit and

the first two data bytes are used for acceptance filtering.

Messages may also be accepted if there are no data bytes

existing due to a set RTR bit or if there is none or only one

data byte because of the corresponding data length code.

For a successful reception of a message, all single bit

comparisons have to signal acceptance.

Note, that the 4 least significant bits of AMR1 and ACR1

are not used. In order to be compatible with future products

these bits should be programmed to be ‘don’t care’ by

setting AMR1.3, AMR1.2, AMR1.1 and AMR1.0 to logic 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935230900112 | 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, PDIP28 |

| 06NU06NU | INNENGEWINDE BSP DREHB G 0.38 |

| 08NU06NU | INNENGEWINDE BSP DREHB G G 0.38X0.5ZOLL |

| 08NU08NU | INNENGEWINDE BSP DREHB G 0.5 |

| 08NU10NU | INNENGEWINDE BSP DREHB G 0.5X0.63ZOLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

| 935252-5 | 制造商:C-H 功能描述:935252-5 |

| 935257650112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY ICSUBS TO 935257650112 |

| 935260093112 | 制造商:NXP Semiconductors 功能描述:IC AVIC ADV BASESTATION 14SOIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。