- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24624 > 9250BF-27LFT (INTEGRATED DEVICE TECHNOLOGY INC) 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 9250BF-27LFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.300 INCH, 0.025 INCH PITCH, GREEN, MO-118, SSOP-56 |

| 文件頁(yè)數(shù): | 5/17頁(yè) |

| 文件大?。?/td> | 221K |

| 代理商: | 9250BF-27LFT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

13

ICS9250-27

0395D—10/25/05

1.

The ICS clock generator is a slave/receiver, I

2C component. It can read back the data stored in the latches for

verification. Read-Back will support Intel PIIX4 "Block-Read" protocol.

2.

The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3.

The input is operating at 3.3V logic levels.

4.

The data byte format is 8 bit bytes.

5.

To simplify the clock generator I

2C interface, the protocol is set to use only "Block-Writes" from the controller.

The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any

complete byte has been transferred. The Command code and Byte count shown above must be sent, but the

data is ignored for those two bytes. The data is loaded until a Stop sequence is issued.

6.

At power-on, all registers are set to a default condition, as shown.

General I

2C serial interface information

The information in this section assumes familiarity with I

2C programming.

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

How to Read:

Controller (host) will send start bit.

Controller (host) sends the read address D3

(H)

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

Notes:

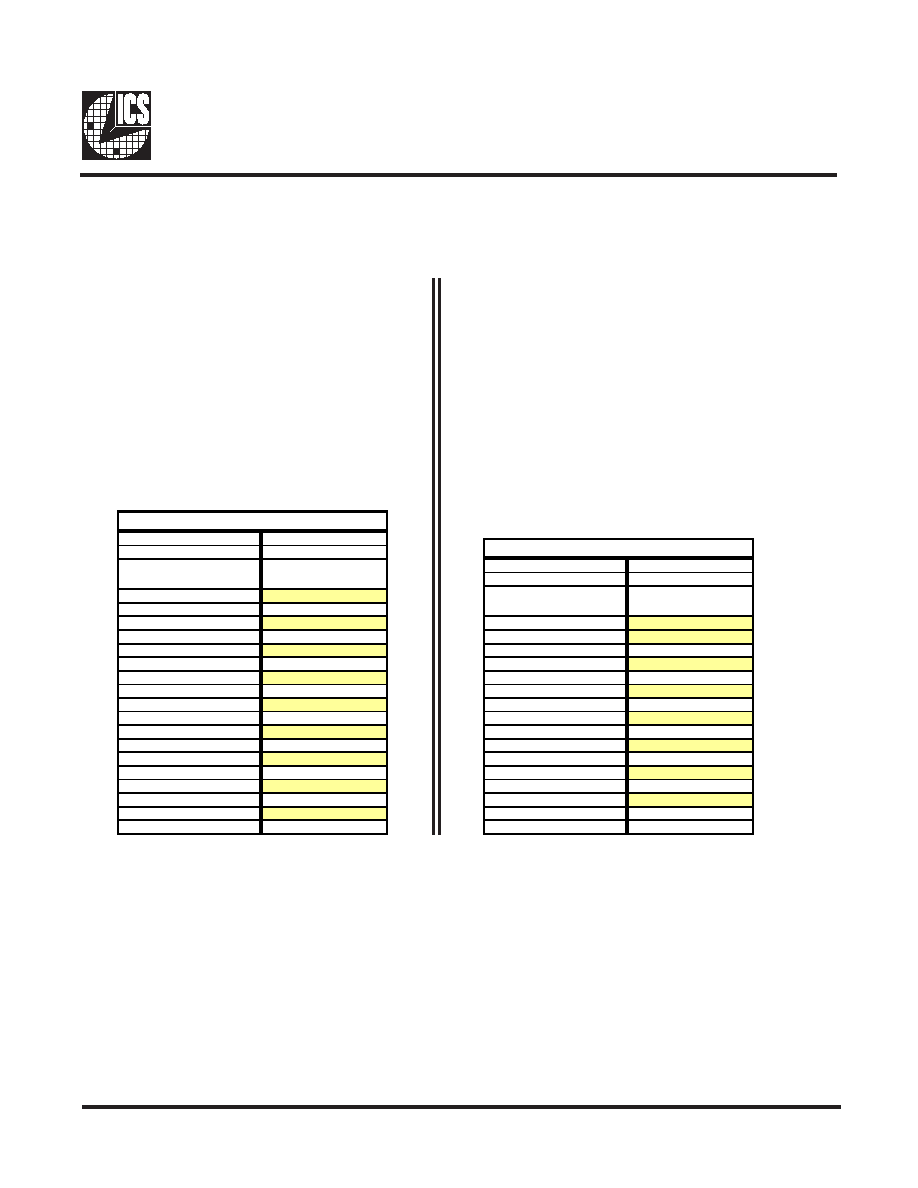

Controller (Host)

ICS (Slave/Receiver)

Start Bit

Address

D3(H)

ACK

Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Stop Bit

How to Read:

Controller (Host)

ICS (Slave/Receiver)

Start Bit

Address

D2(H)

ACK

Dummy Command Code

ACK

Dummy Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Stop Bit

How to Write:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 051-928-9029 | RF Coaxial Connectors |

| 9250BF-28-T | 133.32 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250CF-10 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250CF-10LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 925387-1 | WIRE TERMINAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9250BF-28LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP Tube |

| 9250BF-28LFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP T/R |

| 9250BFI-27LF | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9250BFI-27LFT | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9250CF-08LF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9250CF-08LF PHASED LOCKED LOOP (PLL) - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 9250CF-08LF Phased Locked Loop (PLL) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。