- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369350 > 78P2253-IGT (Electronic Theatre Controls, Inc.) XTAL CER SMT 11X5 4PAD PDF資料下載

參數(shù)資料

| 型號(hào): | 78P2253-IGT |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | XTAL CER SMT 11X5 4PAD |

| 中文描述: | 收發(fā)器 |

| 文件頁(yè)數(shù): | 2/23頁(yè) |

| 文件大?。?/td> | 107K |

| 代理商: | 78P2253-IGT |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

78P2253

E4/STM-1/STS-3/OC-3

Transceiver

2

FUNCTIONAL DESCRIPTION

The 78P2253 contains all the necessary transmit

and receive circuitry for connection between

139.264Mbit/s or 155.52Mbit/s signals and digital

Framer/Deframer ICs.

Operating Rate

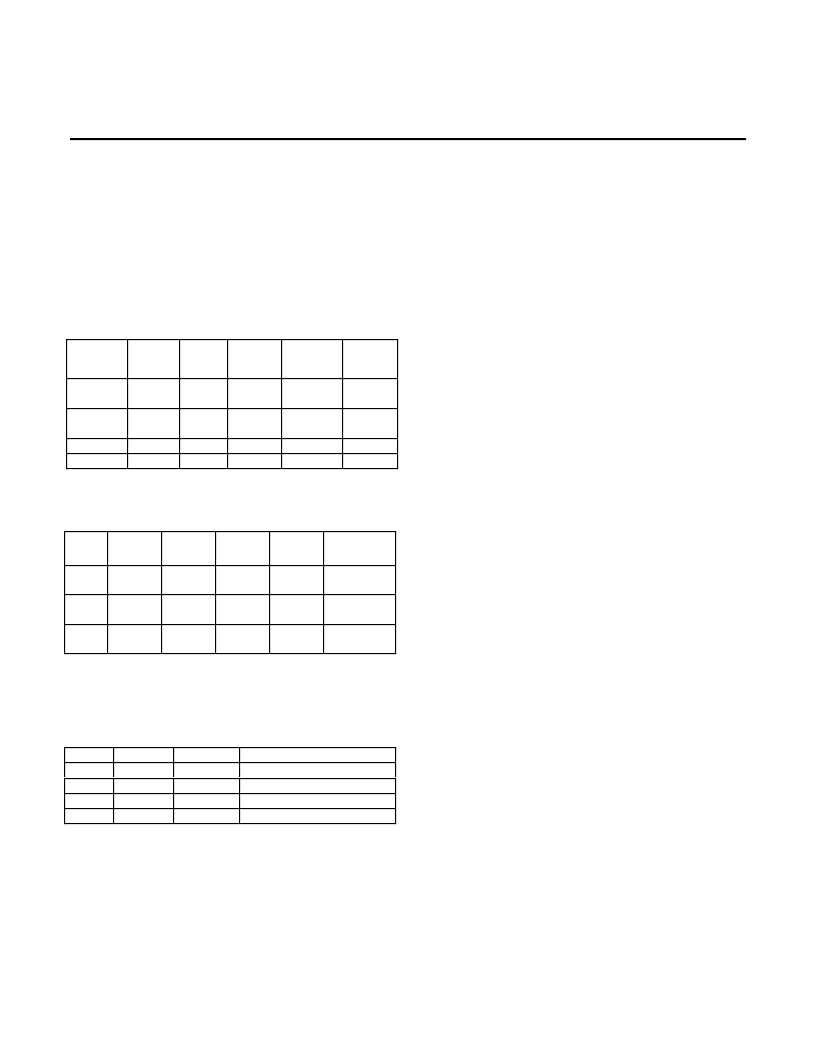

The 78P2253 has a variety of operating modes and

rates. They are summarized in the tables below.

More detailed descriptions can be found in the

sections that follow.

Standard

E4/

SONET

CMI/

ECL

Rate

(Mbit/s)

Reference

Frequency

(MHz)

Active I/O

OC-3

STM1 optic

0

0

155.52

19.44

ECL

STS-3

STM-1 Coax

0

1

155.52

19.44

CMI

1

0

139.264

17.408

ECL

E4

1

1

139.264

17.408

CMI

The digital interface of the 78P2253 can be either

Serial PECL, 4-bit Parallel CMOS or 8-bit Parallel

CMOS.

Mode

PAR/

SER

8BIT/

BIT

Data pins

Clock

pins

Clock

Frequency

(MHz)

Serial

0

X

TXDTP,N

RXDTP,N

TXCKP,N

RXCKP,N

155.52(Sonet)

139.264 (E4)

4-bit

Parallel

1

0

TXDT[3:0]

RXDT[3:0]

TXCK

RXCK

38.88(Sonet)

34.816(E4)

8-bit

Parallel

1

1

TXDT[7:0]

RXDT[7:0]

TXCK

RXCK

19.44(Sonet)

17.408(E4)

Transmit timing is derived from either the reference

clock (the crystal oscillator or CKIN), or the

recovered receive clock. LLBACK and RLBACK

control the local and remote loopback modes

respectively.

LLBACK

RLBACK

HUB/

HOST

Transmit Clock derived from

0

0

1

Reference

1

0

1

Reference

X

1

1

Receiver

X

X

0

Receiver

Medium Choices

The CMI/

ECL

pin selects one of two media for

transmission.

When the CMI/

ECL

pin is high, the chip is in CMI

mode and a 75

coaxial cable is used as the

transmission medium. In this mode, the CMIOUTP

and CMIOUTN pins are active. They connect the

chip to the coaxial cable through a transformer and

matching resistors. In CMI mode the transmitter

shapes the transmit pulses to meet the appropriate

template and the adaptive equalizer corrects the

received signal for dispersive attenuation. The

ECLOUTP and ECLOUTN pins are inoperative and

should be left open.

When the CMI/

ECL

pin is low the chip is in ECL

mode and a fiber optics transceiver is used. The

output data signal from the pins ECLOUTP and

ECLOUTN have PECL levels. In this mode, the CMI

pins are inoperative and should be left open. The

CMI encoder and decoder are disabled.

TRANSMITTER OPERATION

The transmitter section generates an analog signal

for transmission through a transformer onto the

coaxial cable or fiber optic module.

When the PAR/

SER

pin is low the chip is in serial

mode. Serial data is input to the 78P2253 on the

TXDTP and TXDTN pins at PECL levels. The data is

timed with the clock generated by the 78P2253 on

the TXCKP and TXCKN pins. In this mode the

8BIT/

$BIT

pin is ignored.

When the PAR/SER pin is high the chip is in parallel

mode. Parallel data is in put to the 78P2253 on the

TXDT[7:0] pins. The input data is timed with the

clock output from TXCK. When 8BIT/

$BIT

is high all

eight bits of TXDT[7:0] are used and the clock

frequency at TXCK is one-eighth the standard

frequency. When 8BIT/

$BIT

is low the lower four

bits, TXCK[3:0] are used and TXCK is one-fourth the

standard frequency.

The first bit output from the ECL/CMI interface is the

most significant bit on the parallel interface, TXDT7

in eight bit mode, TXDT3 in four bit mode.

The clock is generated by a phase-locked oscillator

(PLO). The PLO is locked to a crystal oscillator

operating at one-eighth of the standard clock

frequency, 19.44MHz for OC-3, STS-3 and STM-1

and 17.408MHz for E4. This is shown in Figure 1a.

An external clock signal at CKIN may also be

substituted for a crystal as the reference frequency

for the chip. In this mode, XTL1 and XTL2 must be

configured as shown in Figure 1b. Note that the chip

can be in either ECL or CMI mode when using either

an external clock or a crystal for the reference. In

serial mode the reference clock is output from

TXCK. In parallel mode, the parallel transmit clock is

output from TXCK.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 78P7200 | Line Interface Unit |

| 78P7200-IH | Line Interface Unit |

| 78P7200 | E3/DS3/STS-1 Transceiver |

| 78P7200L | E3/DS3/STS-1 Transceiver |

| 78P7200L-IGT | E3/DS3/STS-1 Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 78P2254 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:OC-3 / STM-1 / STS-3 / E4 Transceivers |

| 78P2254-IGT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| 78P2342-IGT | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:2-port E3/DS3/STS-1 LIU with Jitter Attenuator |

| 78P2342-IGT/A07 | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:2-port E3/DS3/STS-1 LIU with Jitter Attenuator |

| 78P2342-IGT/F | 制造商:Maxim Integrated Products 功能描述:LEAD FREE - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。