- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360456 > 74HC109PW (NXP SEMICONDUCTORS) Dual JK flip-flop with set and reset; positive-edge trigger PDF資料下載

參數(shù)資料

| 型號(hào): | 74HC109PW |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual JK flip-flop with set and reset; positive-edge trigger |

| 中文描述: | HC/UH SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO16 |

| 文件頁(yè)數(shù): | 5/9頁(yè) |

| 文件大小: | 65K |

| 代理商: | 74HC109PW |

1997 Nov 25

5

Philips Semiconductors

Product specification

Dual JK flip-flop with set and reset;

positive-edge trigger

74HC/HCT109

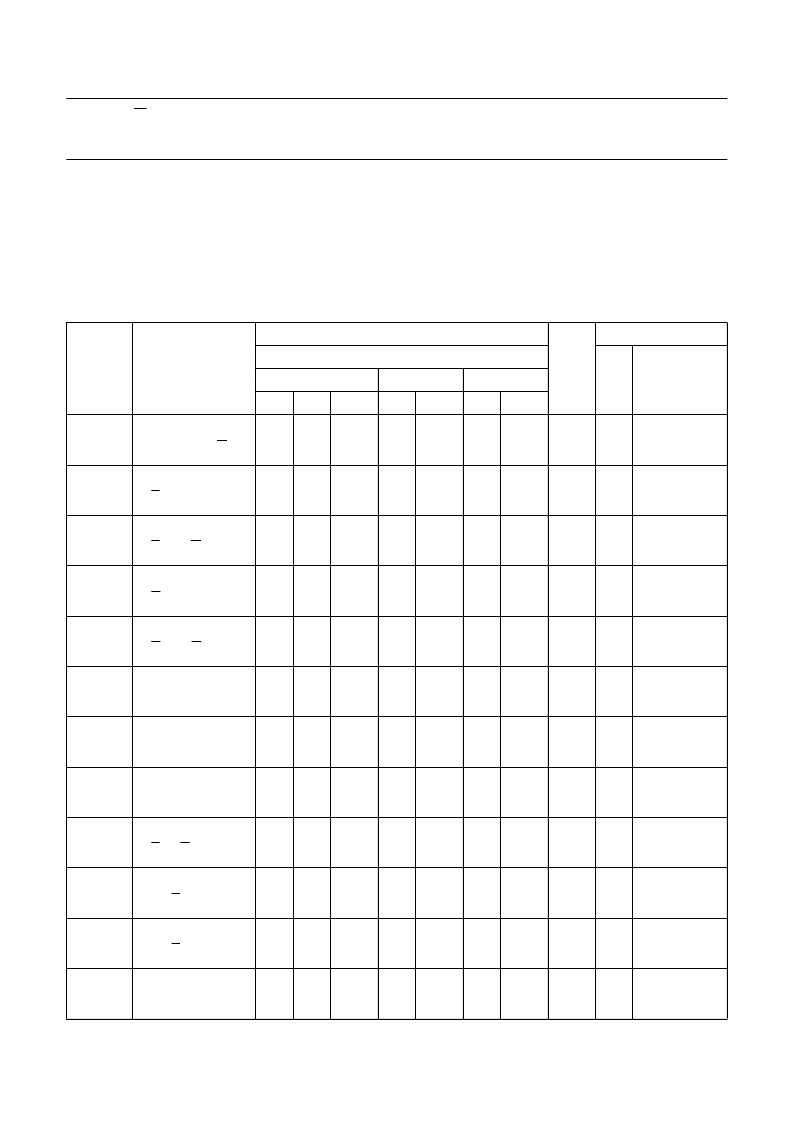

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see

“74HC/HCT/HCU/HCMOS Logic Family Specifications”

.

Output capability: standard

I

CC

category: flip-flops

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL

PARAMETER

T

amb

(

°

C)

TEST CONDITIONS

74HC

UNIT

V

CC

(V)

WAVEFORMS

+

25

40 to

+

85

40 to

+

125

min.

typ.

50

18

14

30

11

9

41

15

12

41

15

12

39

14

11

19

7

6

19

7

6

14

5

4

19

7

6

17

6

5

0

0

0

22

68

81

max.

175

35

30

120

24

20

155

31

26

185

37

31

170

34

29

75

15

13

min.

max.

220

44

37

150

30

26

195

39

33

230

46

39

215

43

37

95

19

16

min.

max.

265

53

45

180

36

31

235

47

40

280

56

48

255

51

43

110

22

19

t

PHL

/ t

PLH

propagation delay

nCP to nQ, nQ

ns

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

Fig.6

t

PLH

propagation delay

nS

D

to nQ

ns

Fig.7

t

PHL

propagation delay

nS

D

to nQ

ns

Fig.7

t

PHL

propagation delay

nR

D

to nQ

ns

Fig.7

t

PLH

propagation delay

nR

D

to nQ

ns

Fig.7

t

THL

/ t

TLH

output transition

time

ns

Fig.6

t

W

clock pulse width

HIGH or LOW

80

16

14

80

16

14

70

14

12

70

14

12

5

5

5

6.0

30

35

100

20

17

100

20

17

90

18

15

90

18

15

5

5

5

5.0

24

28

120

24

20

120

24

20

105

21

18

105

21

18

5

5

5

4.0

20

24

ns

Fig.6

t

W

set or reset pulse

width HIGH or LOW

ns

Fig.7

t

rem

removal time

nS

D

, nR

D

to nCP

ns

Fig.7

t

su

set-up time

nJ, nK to nCP

ns

Fig.6

t

h

hold time

nJ, nK to nCP

ns

Fig.6

f

max

maximum clock

pulse frequency

MHz

Fig.6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74HC112 | Dual JK flip-flop with set and reset; negative-edge trigger |

| 74HCT112 | 8-Line To 3-Line Priority Encoders 16-SO -40 to 85 |

| 74HC11 | Triple 3-input AND gate |

| 74HCT11 | 8-Line To 3-Line Priority Encoders 16-SO -40 to 85 |

| 74HC123 | Dual retriggerable monostable multivibrator with reset |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74HC10D | 功能描述:邏輯門 TRIPLE 3-INPUT NAND GATE RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| 74HC10D,652 | 功能描述:邏輯門 TRIPLE 3-INPUT NAND RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| 74HC10D,653 | 功能描述:邏輯門 TRIPLE 3-INPUT NAND GATE RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| 74HC10D,653-CUT TAPE | 制造商:NXP 功能描述:74HC10 Series 6 V High-Speed Si-Gate CMOS Triple 3-Input NAND Gate - SOIC-14 |

| 74HC10D | 制造商:NXP Semiconductors 功能描述:IC 74HC CMOS SMD 74HC10 SOIC14 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。