- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384065 > μPD703003 (NEC Corp.) 16/32 Bit Single Chip Microcontrollers(16/32位單片微控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | μPD703003 |

| 廠商: | NEC Corp. |

| 英文描述: | 16/32 Bit Single Chip Microcontrollers(16/32位單片微控制器) |

| 中文描述: | 16/32位單片機(jī)微控制器(16/32位單片微控制器) |

| 文件頁(yè)數(shù): | 19/82頁(yè) |

| 文件大小: | 592K |

| 代理商: | ΜPD703003 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

19

μ

PD703003

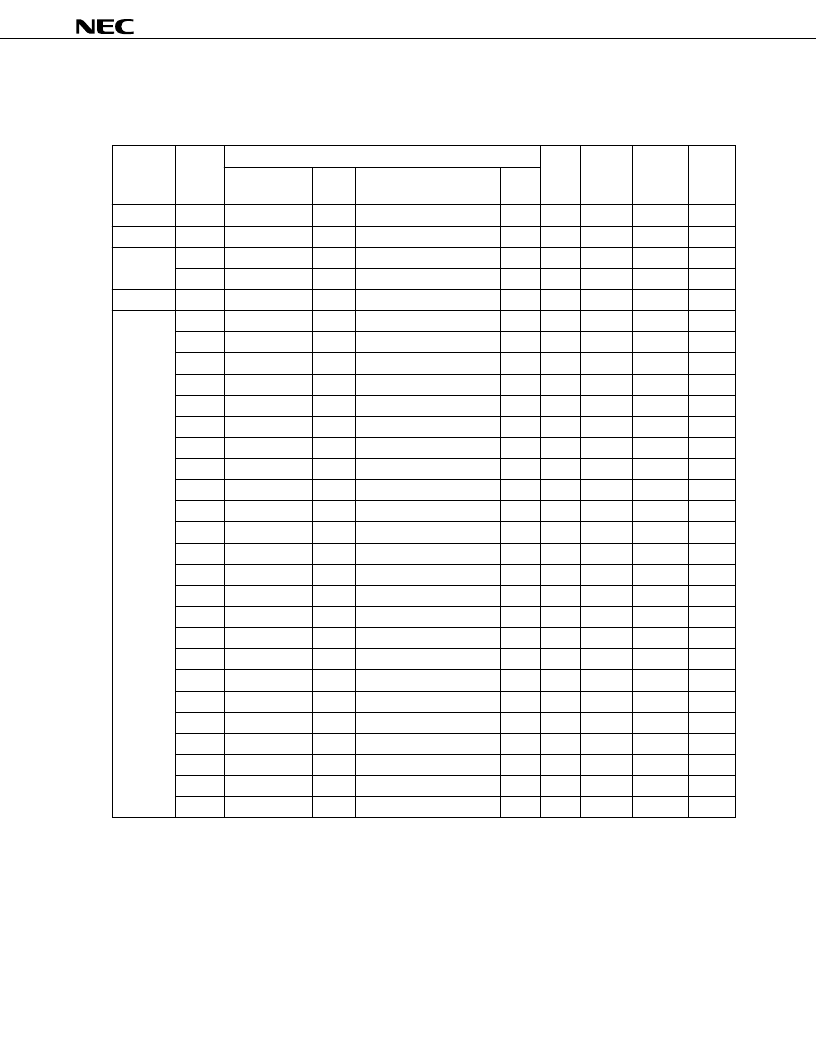

Interrupt/exception sources are shown in Table 6-1.

Table 6-1. List of Interrupts (1/2)

Interrupt/Exception Source

Default

Exception

Handler

Restored

Type

Category

Name

Control

Register

Trigger Source

Unit

Priority

Level

Code

Address

PC

Reset

Interrupt

RESET

—

Reset input

—

—

0000H

00000000H

Undefined

Nonmaskable

Interrupt

NMI

—

NMI input

—

—

0010H

00000010H

nextPC

Software

exception

Exception

TRAP0n

Note

—

TRAP instruction

—

—

004nH

Note

00000040H

nextPC

Exception

TRAP1n

Note

—

TRAP instruction

—

—

005nH

Note

00000050H

nextPC

Exception trap

Exception

ILGOP

—

Undefined instruction code

—

—

0060H

00000060H

nextPC

Maskable

Interrupt

INTOV11

OVIC11

Timer 11 overflow

RPU

0

0080H

00000080H

nextPC

Interrupt

INTOV12

OVIC12

Timer 12 overflow

RPU

1

0090H

00000090H

nextPC

Interrupt

INTOV13

OVIC13

Timer 13 overflow

RPU

2

00A0H

000000A0H

nextPC

Interrupt

INTOV14

OVIC14

Timer 14 overflow

RPU

3

00B0H

000000B0H

nextPC

Interrupt

INTP110/INTCC110

P11IC0

Match between INTP110 and CC110

Pin/RPU

4

00C0H

000000C0H

nextPC

Interrupt

INTP111/INTCC111

P11IC1

Match between INTP111 and CC111

Pin/RPU

5

00D0H

000000D0H

nextPC

Interrupt

INTP112/INTCC112

P11IC2

Match between INTP112 and CC112

Pin/RPU

6

00E0H

000000E0H

nextPC

Interrupt

INTP113/INTCC113

P11IC3

Match between INTP113 and CC113

Pin/RPU

7

00F0H

000000F0H

nextPC

Interrupt

INTP120/INTCC120

P12IC0

Match between INTP120 and CC120

Pin/RPU

8

0100H

00000100H

nextPC

Interrupt

INTP121/INTCC121

P12IC1

Match between INTP121 and CC121

Pin/RPU

9

0110H

00000110H

nextPC

Interrupt

INTP122/INTCC122

P12IC2

Match between INTP122 and CC122

Pin/RPU

10

0120H

00000120H

nextPC

Interrupt

INTP123/INTCC123

P12IC3

Match between INTP123 and CC123

Pin/RPU

11

0130H

00000130H

nextPC

Interrupt

INTP130/INTCC130

P13IC0

Match between INTP130 and CC130

Pin/RPU

12

0140H

00000140H

nextPC

Interrupt

INTP131/INTCC131

P13IC1

Match between INTP131 and CC131

Pin/RPU

13

0150H

00000150H

nextPC

Interrupt

INTP132/INTCC132

P13IC2

Match between INTP132 and CC132

Pin/RPU

14

0160H

00000160H

nextPC

Interrupt

INTP133/INTCC133

P13IC3

Match between INTP133 and CC133

Pin/RPU

15

0170H

00000170H

nextPC

Interrupt

INTP140/INTCC140

P14IC0

Match between INTP140 and CC140

Pin/RPU

16

0180H

00000180H

nextPC

Interrupt

INTP141/INTCC141

P14IC1

Match between INTP141 and CC141

Pin/RPU

17

0190H

00000190H

nextPC

Interrupt

INTP142/INTCC142

P14IC2

Match between INTP142 and CC142

Pin/RPU

18

01A0H

000001A0H

nextPC

Interrupt

INTP143/INTCC143

P14IC3

Match between INTP143 and CC143

Pin/RPU

19

01B0H

000001B0H

nextPC

Interrupt

INTCM4

CMIC4

Signal matches CM4

RPU

20

01C0H

000001C0H

nextPC

Interrupt

INTCSI0

CSIC0

CSI0 send/receive completion

SIO

21

01D0H

000001D0H

nextPC

Interrupt

INTCSI1

CSIC1

CSI1 send/receive completion

SIO

22

01E0H

000001E0H

nextPC

Interrupt

INTCSI2

CSIC2

CSI2 send/receive completion

SIO

23

01F0H

000001F0H

nextPC

Note

n represents a value between 0 and FH.

Remarks 1.

Default priority:The default priority level is the level that takes precedence when multiple

maskable interrupt requests having the same priority level occur at the same

time. The highest priority level is level 0.

Restored PC:This is the PC value that is saved to EIPC or FEPC when interrupt or exception

handling is activated. However, if an interrupt occurs during execution of the

DIVH (divide) instruction, the recovered PC value is the PC value of the current

instruction (DIVH).

2.

The invalid instruction execution address can be obtained (using restored PC-4) when an invalid

instruction code exception occurs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD703100 | 32 Bit RISC Microcontrollers(32 位 RISC 微控制器) |

| μPD703101 | 32 Bit RISC Microcontrollers(32 位 RISC 微控制器) |

| μPD70F3102 | 32 Bit RISC Microcontrollers(32 位 RISC 微控制器) |

| μPD705101GM-100-8ED | 32 Bit RISC Microcontrollers(32位RISC微控制器) |

| μPD70P3002 | 16/32 Single -Chip Microcontroller(16/32 位單片微控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD7035 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:FOR OPTICAL COMMUNICATION |

| PD7087 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:InGaAs PIN PHOTO DIODES |

| PD7088 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:InGaAs PIN PHOTO DIODES |

| PD708C7 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:InGaAs PIN PHOTO DIODES |

| PD708C8 | 制造商:MITSUBISHI 制造商全稱(chēng):Mitsubishi Electric Semiconductor 功能描述:InGaAs PIN PHOTO DIODES |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。