- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16988 > XRD98L61ZEVAL (Exar Corporation)EVAL BOARD FOR XRD98L61AIV PDF資料下載

參數(shù)資料

| 型號: | XRD98L61ZEVAL |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 2/38頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XRD98L61AIV |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

XRD98L61

10

Rev. 2.00

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Offset

OB[7]

OB[6]

OB[5]

OB[4]

OB[3]

OB[2]

OB[1]

OB[0]

Default

0

1

0

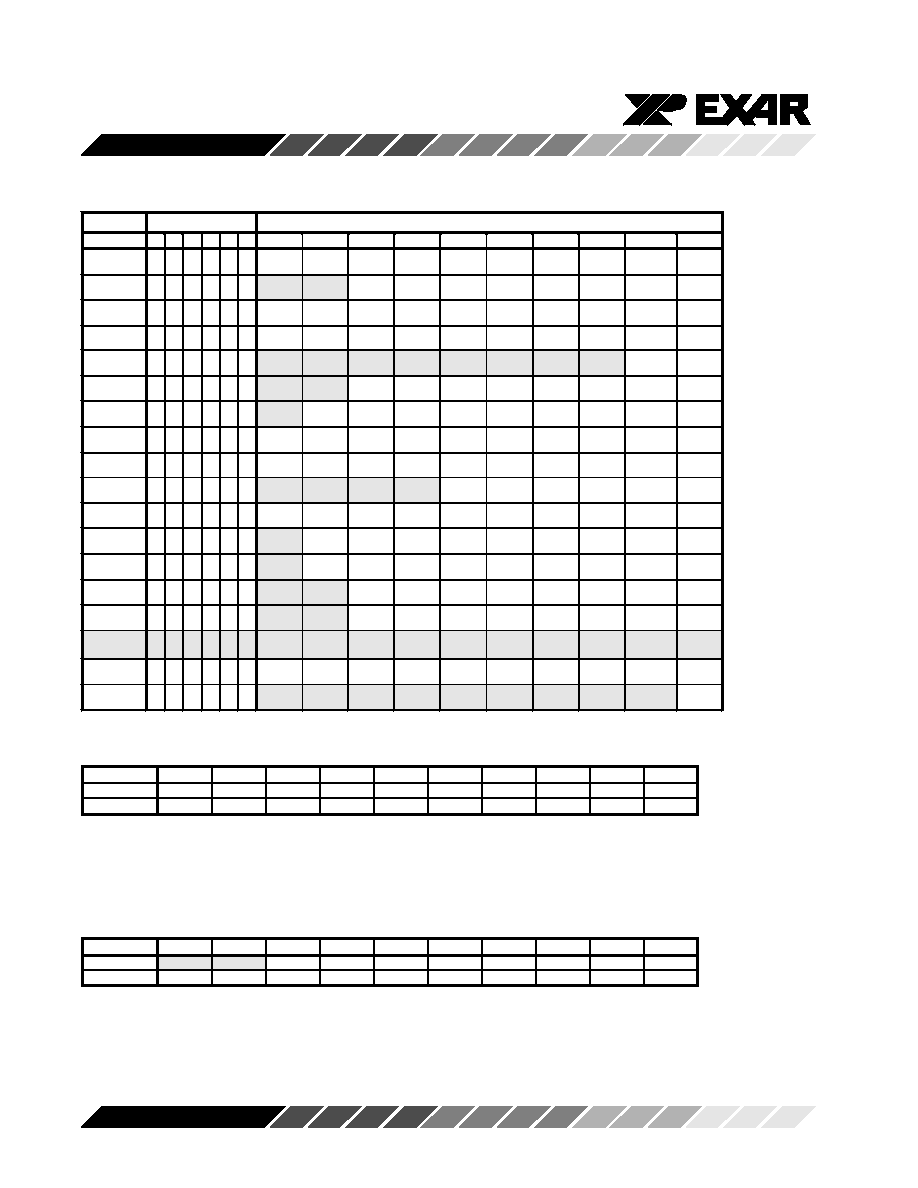

Offset Register (Reg. 1, Address 000001)

The Offset register is used to set the target ADC output code for Optical Black pixels.

See the Black Level Offset Calibration section for more information.

Table 1. Serial Interface Register Address Map & default values

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Gain

PGA[9]

PGA[8]

PGA[7]

PGA[6]

PGA[5]

PGA[4]

PGA[3]

PGA[2]

PGA[1]

PGA[0]

Default

0

The Gain register is used to set the gain of the Programmable Gain Amplifier (PGA).

Code 0000000000 is minimum gain (0 dB). Codes 1011111111 and greater are maximum gain (36 dB).

See the Programmable Gain Amplifier (PGA) section for more information.

Gain Register (Reg. 0, Address 000000)

Address bits

Data bits

Reg. Name A5 A4 A3 A2 A1 A0

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Gain

0 0 0

PGA[9]

0

PGA[8]

0

PGA[7]

0

PGA[6]

0

PGA[5]

0

PGA[4]

0

PGA[3]

0

PGA[2]

0

PGA[1]

0

PGA[0]

0

Offset

0 0 0

0 0 1

OB[7]

1

OB[6]

0

OB[5]

0

OB[4]

0

OB[3]

0

OB[2]

0

OB[1]

0

OB[0]

0

Calibration

0 0 0

0 1 0

Avg[2]

1

Avg[1]

0

Avg[0]

1

Mode

0

LFrame

0

DNS[1]

1

DNS[0]

1

FastCal

1

Hold

0

ManCal

0

Wait A

0 0 0

0 1 1

WL[11]

0

WL[10]

0

WL[9]

0

WL[8]

0

WL[7]

0

WL[6]

0

WL[5]

0

WL[4]

0

WL[3]

0

WL[2]

0

Wait B

0 0 0

1 0 0

WL[1]

0

WL[0]

1

OB Lines

0 0 0

1 0 1

OBL[7]

0

OBL[6]

0

OBL[5]

0

OBL[4]

0

OBL[3]

0

OBL[2]

0

OBL[1]

1

OBL[0]

0

CDAC

0 0 0

1 1 0

CDAC[8]

0

CDAC[7]

0

CDAC[6]

0

CDAC[5]

0

CDAC[4]

0

CDAC[3]

0

CDAC[2]

0

CDAC[1]

0

CDAC[0]

0

FDAC

0 0 0

1 1 1

FDAC[9]

0

FDAC[8]

0

FDAC[7]

0

FDAC[6]

0

FDAC[5]

0

FDAC[4]

0

FDAC[3]

0

FDAC[2]

0

FDAC[1]

0

FDAC[0]

0

Control

0 0 1

0 0 0

DIGtest

0

ADCtest

0

NoCDS

0

LowPwr

0

OE

1

DAC1pd

1

DAC0pd

1

AFEpd

0

ADCpd

0

PwrDwn

0

Polarity

0 0 1

SBLKpol

0

SPIXpol

0

CALpol

0

CLAMPpol

0

*Reserved

0

ADCpol

0

Clock

0 0 1

0 1 0

CLKtest

0

Nullamp

0

CMtest

0

Fastclk

0

CLAMPopt

0

OneShot

0

ClampCal

0

SPIXopt

0

RSTreject

0

VSreject

0

Delay A

0 0 1

0 1 1

DelayA[8]

0

DelayA[7]

0

DelayA[6]

0

DelayA[5]

0

DelayA[4]

0

DelayA[3]

0

DelayA[2]

0

DelayA[1]

0

DelayA[0]

0

Delay B

0 0 1

1 0 0

DelayB[8]

0

DelayB[7]

0

DelayB[6]

0

DelayB[5]

0

DelayB[4]

0

DelayB[3]

0

DelayB[2]

0

DelayB[1]

0

DelayB[0]

0

DAC0

0 0 1

1 0 1

DAC0[7]

0

DAC0[6]

0

DAC0[5]

0

DAC0[4]

0

DAC0[3]

0

DAC0[2]

0

DAC0[1]

0

DAC0[0]

0

DAC1

0 0 1

1 1 0

DAC1[7]

0

DAC1[6]

0

DAC1[5]

0

DAC1[4]

0

DAC1[3]

0

DAC1[2]

0

DAC1[1]

0

DAC1[0]

0

ReadBack

1 1 1

1 1 0

RBenable

0

RBreg[8]

0

RBreg[7]

0

RBreg[6]

0

RBreg[5]

0

RBreg[4]

0

RBreg[3]

0

RBreg[2]

0

RBreg[1]

0

RBreg[0]

0

Reset

1 1 1

Reset

0

NOTE: *Reserved Test register bit. Used for factory test only. Please do not modify.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LGU2G391MELB | CAP ALUM 390UF 400V 20% SNAP |

| ECC31DCMT | CONN EDGECARD 62POS .100 WW |

| 1589448-3 | STRIP CON |

| AD8335-EVALZ | BOARD EVALUATION FOR AD8335 |

| RSM06DRSI-S288 | CONN EDGECARD 12POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRD98L62 | 制造商:EXAR 制造商全稱:EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L62ACV | 制造商:EXAR 制造商全稱:EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L62ACV-F | 功能描述:視頻 IC RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRD98L62EVAL | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開發(fā)工具 XRD98L62 EVAL BOARD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| XRD98L62ZEVAL | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開發(fā)工具 Eval Board (Solder) XRD98L62AIV RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。