- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16514 > XR17V252IM-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17V252 100TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XR17V252IM-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 58/69頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V252 100TQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

XR17V252

61

REV. 1.0.2

66 MHZ PCI BUS DUAL UART WITH POWER MANAGEMENT SUPPORT

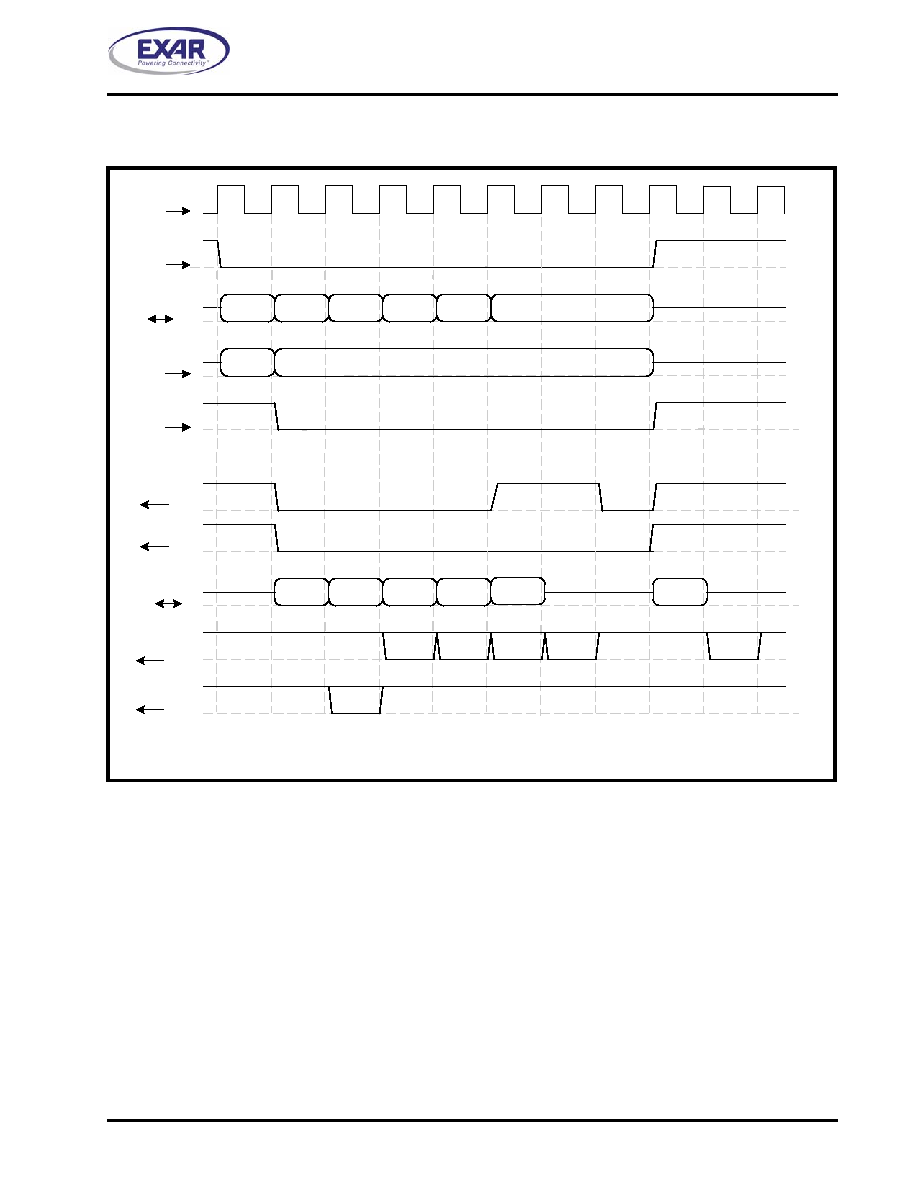

FIGURE 21. DEVICE CONFIGURATION REGISTERS, UART REGISTERS AND TRANSMIT DATA BURST WRITE OPERA-

TION

CLK

FRAME#

AD[31:0]

C/BE[3:0]#

TRDY#

IRDY#

DEVSEL#

1

23

4

Address

Bus

CMD

Byte Enable# = DWORD

PCI BWR

5

6

7

PAR

PERR#

8

Note: PERR# and SERR are optional in a bus target application.

Even Parity is on AD[31:0], C/BE[3:0]#, and PAR

Host

Target

Host

Target

Address

Parity

SERR#

Target

Active

Data

Parity

Active

910

Data

DWORD

Data DWORD

DWO

R

D

T

R

ANSFER

DWO

R

D

T

R

ANSFER

DWO

R

D

T

R

ANSFER

DWO

R

D

T

R

ANSFER

DWO

R

D

T

R

ANSFER

Data

Parity

Data

Parity

Data

Parity

Data

Parity

Active

11

Data

DWORD

Data

DWORD

Data

DWORD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 6278890-4 | C/A 62.5 OFNR MTRJ-MTRJ RED SEC |

| 6374656-4 | C/A LC TO LC MM 2.0MM 4M |

| VE-J5R-EX | CONVERTER MOD DC/DC 7.5V 75W |

| RBC26DRXN | CONN EDGECARD 52POS DIP .100 SLD |

| RBM15DTMN | CONN EDGECARD 30POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17V252IM-F | 功能描述:UART 接口集成電路 66MHz Dual PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V252IMTR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 64Byte FIFO 3.3V 100-Pin TQFP T/R 制造商:Exar Corporation 功能描述:XR17V252IMTR-F |

| XR17V254 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT |

| XR17V254_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT |

| XR17V254IV | 制造商:EXAR 制造商全稱:EXAR 功能描述:66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。