- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16498 > XR16V554DIV-0A-EB (Exar Corporation)EVAL BOARD FOR XR16V554D 64LQFP PDF資料下載

參數(shù)資料

| 型號: | XR16V554DIV-0A-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 19/43頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16V554D 64LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

XR16V554/554D

26

2.25V TO 3.6V QUAD UART WITH 16-BYTE FIFO

REV. 1.0.3

MCR[3]: INT Output Enable

Enable or disable INT outputs to become active or in three-state. This function is associated with the INTSEL

input, see below table for details. This bit is also used to control the OP2# signal during internal loopback

mode. INTSEL pin must be LOW during 68 mode.

Logic 0 = INT (A-D) outputs disabled (three state) in the 16 mode (default). During internal loopback mode,

OP2# is HIGH.

Logic 1 = INT (A-D) outputs enabled (active) in the 16 mode. During internal loopback mode, OP2# is LOW.

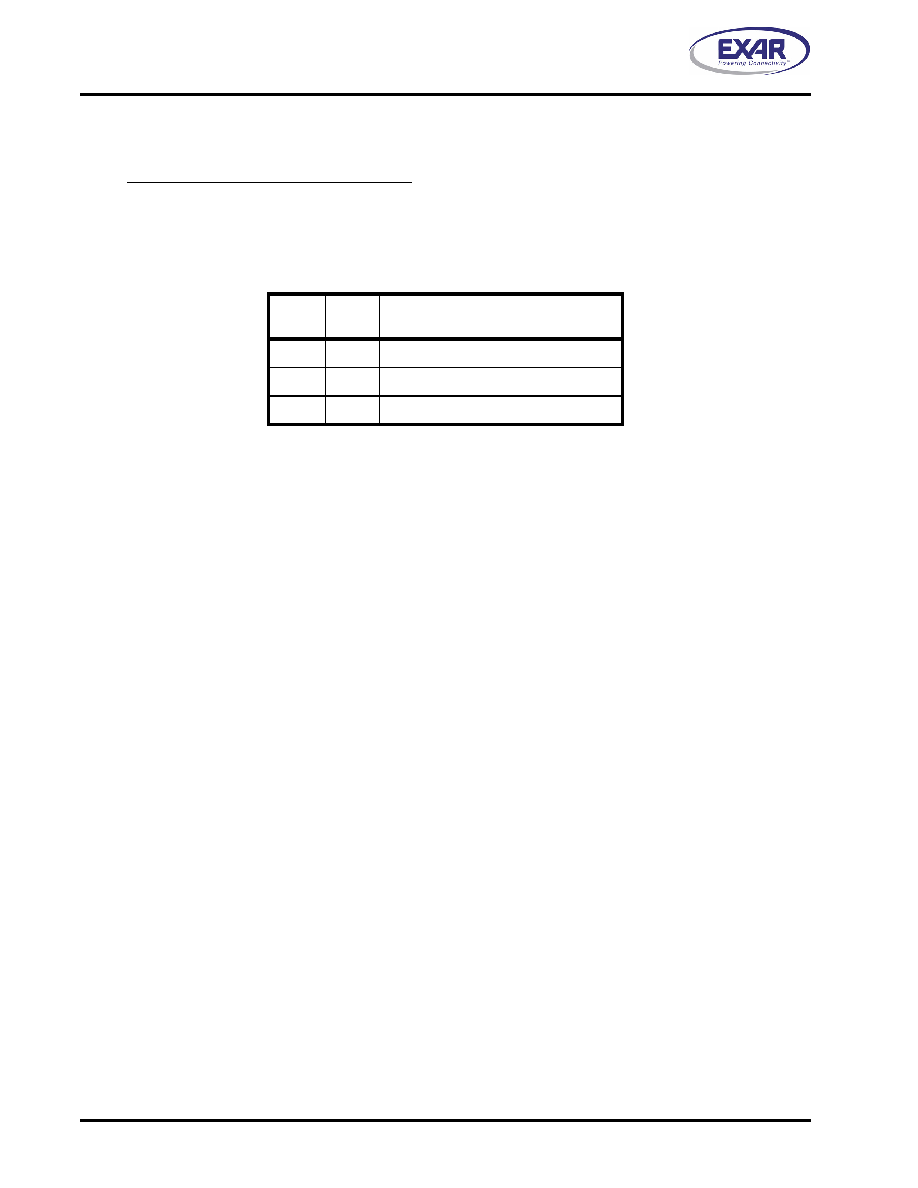

TABLE 12: INT OUTPUT MODES

PIN

BIT-3

INT A-D OUTPUTS IN 16 MODE

0

Three-State

0

1

Active

1

X

Active

MCR[4]: Internal Loopback Enable

Logic 0 = Disable loopback mode (default).

Logic 1 = Enable local loopback mode, see loopback section and Figure 11.

MCR[7:5]: Reserved

4.8

Line Status Register (LSR) - Read/Write

This register is writeable but it is not recommended. The LSR provides the status of data transfers between the

UART and the host. If IER bit-2 is enabled, LSR bit-1 will generate an interrupt immediately and LSR bits 2-4

will generate an interrupt when a character with an error is in the RHR.

LSR[0]: Receive Data Ready Indicator

Logic 0 = No data in receive holding register or FIFO (default).

Logic 1 = Data has been received and is saved in the receive holding register or FIFO.

LSR[1]: Receiver Overrun Flag

Logic 0 = No overrun error (default).

Logic 1 = Overrun error. A data overrun error condition occurred in the receive shift register. This happens

when additional data arrives while the FIFO is full. In this case the previous data in the receive shift register

is overwritten. Note that under this condition the data byte in the receive shift register is not transferred into

the FIFO, therefore the data in the FIFO is not corrupted by the error.

LSR[2]: Receive Data Parity Error Tag

Logic 0 = No parity error (default).

Logic 1 = Parity error. The receive character in RHR does not have correct parity information and is suspect.

This error is associated with the character available for reading in RHR.

LSR[3]: Receive Data Framing Error Tag

Logic 0 = No framing error (default).

Logic 1 = Framing error. The receive character did not have a valid stop bit(s). This error is associated with

the character available for reading in RHR.

INTSEL

MCR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RBC15DCAI-S189 | CONN EDGECARD 30POS R/A .100 SLD |

| 1-6374039-0 | C/A 62.5/125, PLNM ZIP, SC 10 |

| LK1608R82M-T | INDUCTOR MULTILAYER .82UH 0603 |

| VI-J7Y-EZ-S | CONVERTER MOD DC/DC 3.3V 16.5W |

| CBC2016T330M | INDUCTOR POWER 33UH 0806 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16V554DIV-F | 功能描述:UART 接口集成電路 2.25V-3.6V 16B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V554DIVTR-F | 功能描述:UART 接口集成電路 XR16V554DIVTR-F RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V554IJ | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

| XR16V554IJ-0A-EVB | 功能描述:界面開發(fā)工具 Supports V554 68ld PLCC,ISA Interface RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16V554IJ-F | 功能描述:UART 接口集成電路 2.25V-3.6V 16B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。