- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4173 > XC5210-4PQ160C (Xilinx Inc)IC FPGA 324 CLB'S 160-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC5210-4PQ160C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 29/73頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 324 CLB'S 160-PQFP |

| 產(chǎn)品變化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | XC5200 |

| LAB/CLB數(shù): | 324 |

| 邏輯元件/單元數(shù): | 1296 |

| 輸入/輸出數(shù): | 133 |

| 門數(shù): | 16000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 160-BQFP |

| 供應(yīng)商設(shè)備封裝: | 160-PQFP(28x28) |

| 其它名稱: | 122-1145 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

November 5, 1998 (Version 5.2)

7-117

XC5200 Series Field Programmable Gate Arrays

7

.

Note:

1. At power-up, VCC must rise from 2.0 V to VCC min in less then 25 ms, otherwise delay configuration by pulling PROGRAM

Low until VCC is Valid.

2. The first Data byte is loaded and CCLK starts at the end of the first RCLK active cycle (rising edge).

This timing diagram shows that the EPROM requirements are extremely relaxed. EPROM access time can be longer than

500 ns. EPROM data output has no hold-time requirements.

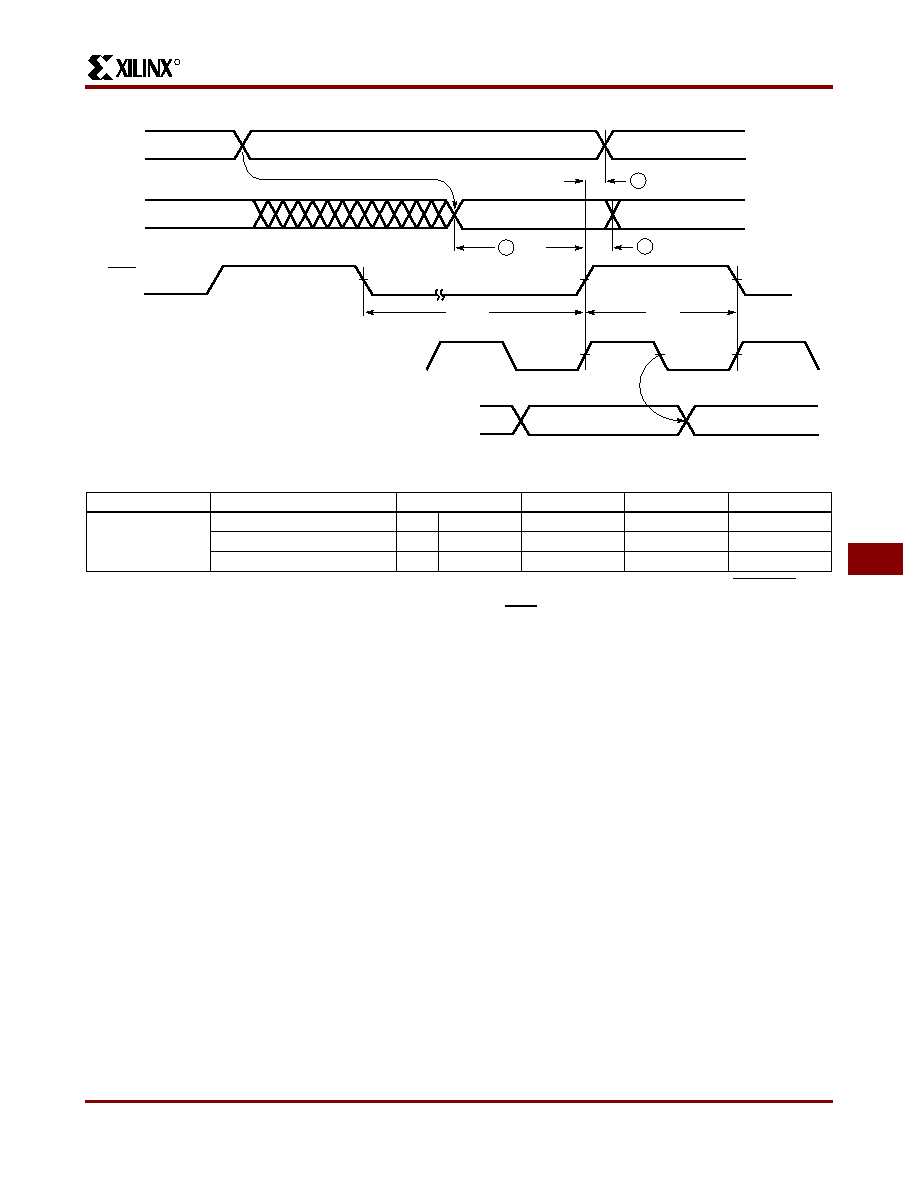

Figure 32: Master Parallel Mode Programming Switching Characteristics

Address for Byte n

Byte

2 TDRC

Address for Byte n + 1

D7

D6

A0-A17

(output)

D0-D7

RCLK

(output)

CCLK

(output)

DOUT

(output)

1 TRAC

7 CCLKs

CCLK

3 TRCD

Byte n - 1

X6078

Description

Symbol

Min

Max

Units

CCLK

Delay to Address valid

1

TRAC

0

200

ns

Data setup time

2

TDRC

60

ns

Data hold time

3

TRCD

0ns

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5204-6PQ160C | IC FPGA 120 CLB'S 160-PQFP |

| ACB66DHAN-S621 | EDGECARD 132POS DIP R/A .050 SLD |

| XC5210-5PQ160C | IC FPGA 324 CLB'S 160-PQFP |

| ACB66DHAD-S621 | EDGECARD 132POS DIP R/A .050 SLD |

| AMM10DREH | CONN EDGECARD 20POS .156 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-4PQ160I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-4PQ208C | 制造商:Xilinx 功能描述: |

| XC5210-4PQ208C0262 | 制造商:Xilinx 功能描述: |

| XC5210-4PQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-4PQ240C | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。