- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359432 > VSC9142 (VITESSE SEMICONDUCTOR CORP) SONET/SDH 2.5Gbps Transport Terminating Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | VSC9142 |

| 廠商: | VITESSE SEMICONDUCTOR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | SONET/SDH 2.5Gbps Transport Terminating Transceiver |

| 中文描述: | MUX/DEMUX, PBGA320 |

| 封裝: | TBGA-320 |

| 文件頁數(shù): | 24/30頁 |

| 文件大?。?/td> | 259K |

| 代理商: | VSC9142 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁

G56054, Rev 1.0

VSC9142

STS-48c Physical Layer Packet/ATMOver SONET/SDH Device

Page 24

1.0 Product Description

.

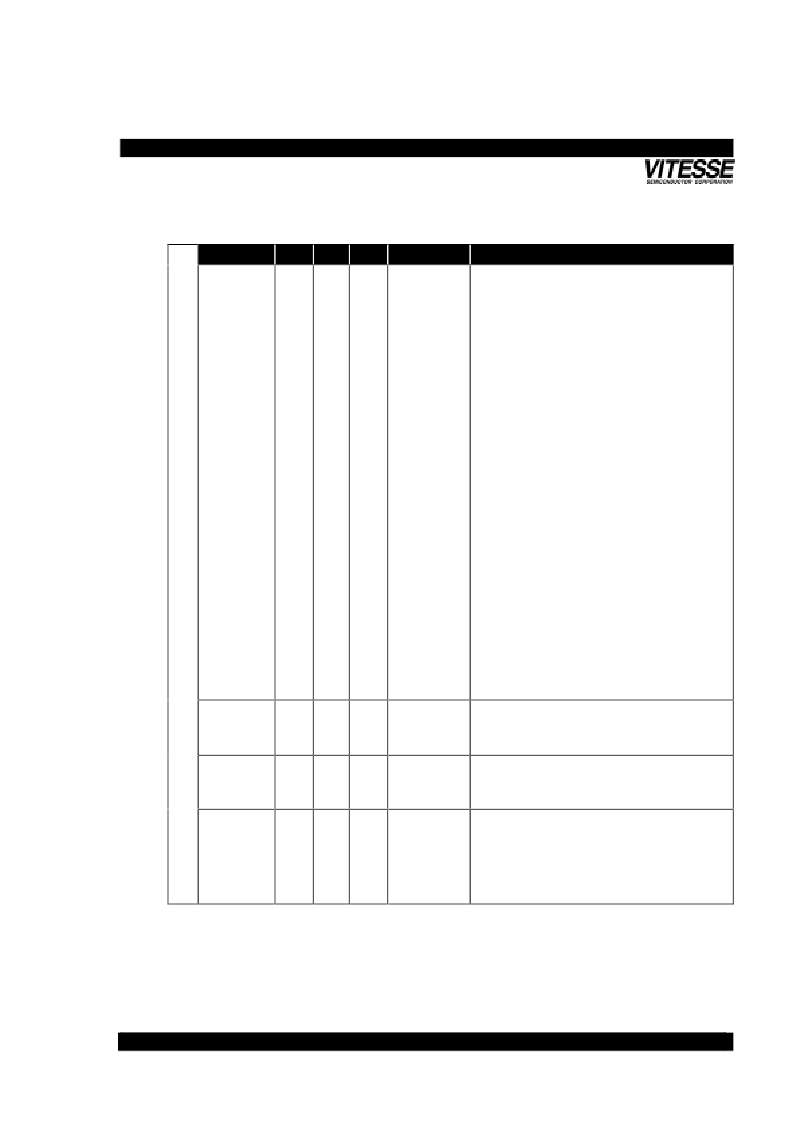

Table 1.1

Hardware Signal Definitions (6 of 12)

Pin Label

RDAT/RUDATA[0]

RDAT/RUDATA[1]

RDAT/RUDATA[2]

RDAT/RUDATA[3]

RDAT/RUDATA[4]

RDAT/RUDATA[5]

RDAT/RUDATA[6]

RDAT/RUDATA[7]

RDAT/RUDATA[8]

RDAT/RUDATA[9]

RDAT/RUDATA[10]

RDAT/RUDATA[11]

RDAT/RUDATA[12]

RDAT/RUDATA[13]

RDAT/RUDATA[14]

RDAT/RUDATA[15]

RDAT/RUDATA[16]

RDAT/RUDATA[17]

RDAT/RUDATA[18]

RDAT/RUDATA[19]

RDAT/RUDATA[20]

RDAT/RUDATA[21]

RDAT/RUDATA[22]

RDAT/RUDATA[23]

RDAT/RUDATA[24]

RDAT/RUDATA[25]

RDAT/RUDATA[26]

RDAT/RUDATA[27]

RDAT/RUDATA[28]

RDAT/RUDATA[29]

RDAT/RUDATA[30]

RDAT/RUDATA[31]

POS Mode:

RPRTY

ATMMode:

RUPRTY

POS Mode:

RMOD[1]

RMOD[0]

Pad

W1

V3

V2

V1

U3

U2

T4

T3

T2

T1

R4

R3

R2

R1

P3

P2

N1

N4

N3

N2

M3

M4

M2

M1

L2

L3

K1

K2

K3

K4

J1

J2

Y3

I/O

O

Type

TTL

Signal Name

Recevie Packet

Data Bus

(RDAT

x

)

or

Receive Cell

Data Bus

(RUDATA

x

)

Description

POS Mode:

This 32-bit data bus is used to drive four-octet true

data fromthe PHY to Packet layer. RDAT[31] is the MSB.

Packets are aligned to the 32-bit RDAT

x

boundary.

ATMMode:

This 32-bit data bus is used to drive four-octet true

data fromthe PHY to ATM layer. RUDATA[31] is the MSB.

O

TTL

Receive Bus

Parity

POS Mode:

RPRTY is the odd/even (programmable, default

odd) parity bit over RDAT[31..0].

ATMMode:

RUPRTY is the odd/even (programmable, default

odd) parity bit over RUDATA[31..0].

POS Mode only:

These outputs are used to qualify RDAT

x

data octets. The state of RMOD[1,0] defines which of the four

RDAT octets contain valid data when REOP is asserted. Non-

EOP words always contain four valid RDAT octets.

POS Mode:

RSOP is asserted (active high) by the Packet layer

to indicate that RDAT

x

contains the first valid octet of a new

packet. The packet interface can be operated without using this

signal.

ATMMode:

RUSOC is asserted (active high) by the ATM layer

to indicate that RUDATA

x

contains the first valid octet of a cell.

This signal is used to support multiple PHY configurations.

W2

W3

O

TTL

Receive Word

Modulo

D

POS Mode:

RSOP

ATMMode:

RUSOC

AA1

O

TTL

Receive Start of

Packet

or

UTOPIA Receive

Start of Cell

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VSC9180 | VSC9180 Arapahoe - 2.5G SONET/SDH Backplane Transceiver |

| VSC9182 | VSC9182 - 40G STS-1 Time Slot Interchange |

| VSC9186 | VSC9186 Killington - Quad STS-48/STM-16 and STS-192/STM-64 Line Interface |

| VSC9187 | VSC9187 Bromley - 3045 x 3045 VT1.5 TSI Switch Fabric |

| VSC9191 | 100 Gbps (40 x 40) SONET/SDH TSI Switch with Dual Rate I/O |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VSC9180 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9180 Arapahoe - 2.5G SONET/SDH Backplane Transceiver |

| VSC9182 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9182 - 40G STS-1 Time Slot Interchange |

| VSC9186 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9186 Killington - Quad STS-48/STM-16 and STS-192/STM-64 Line Interface |

| VSC9186ZB/D | 制造商:Vitesse Semiconductor Corporation 功能描述:CHIPSET |

| VSC9187 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9187 Bromley - 3045 x 3045 VT1.5 TSI Switch Fabric |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。