- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄383982 > UPD703130GC-8EU (NEC Corp.) MOS INTEGRATED CIRCUIT PDF資料下載

參數(shù)資料

| 型號(hào): | UPD703130GC-8EU |

| 廠商: | NEC Corp. |

| 英文描述: | MOS INTEGRATED CIRCUIT |

| 中文描述: | 馬鞍山集成電路 |

| 文件頁(yè)數(shù): | 10/72頁(yè) |

| 文件大?。?/td> | 601K |

| 代理商: | UPD703130GC-8EU |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

Preliminary Data Sheet U15390EJ1V0DS

10

μ

PD703130

(2/2)

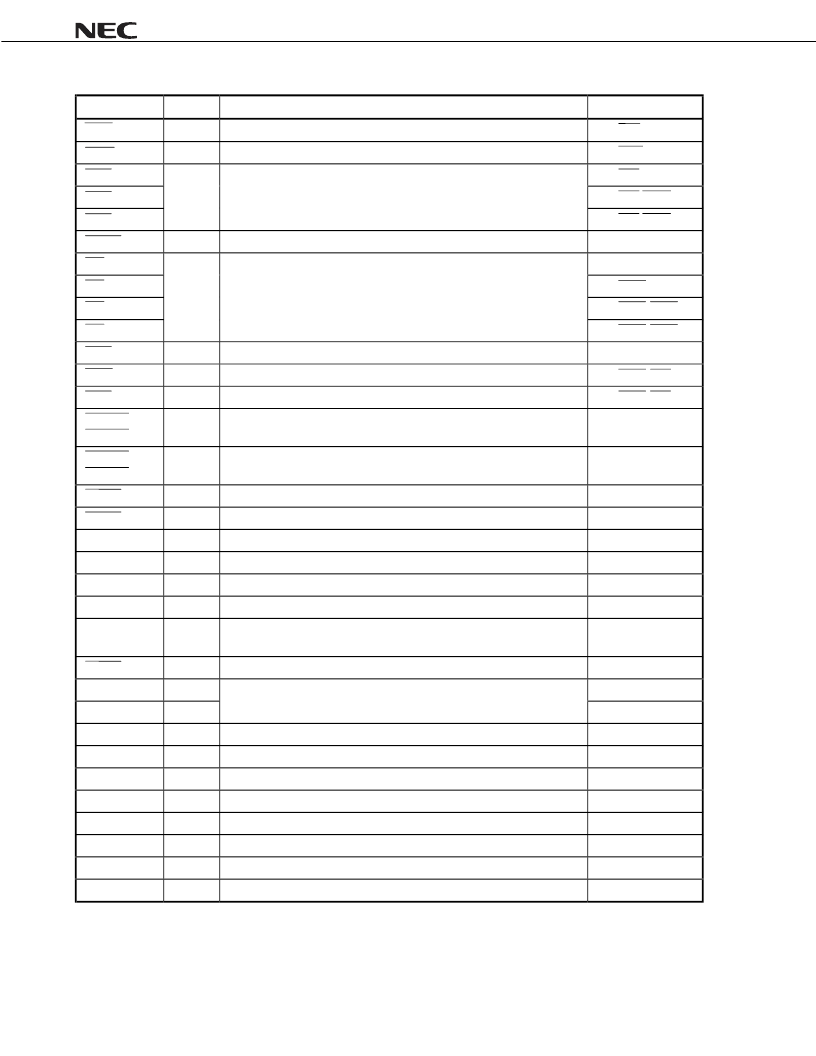

Pin Name

I/O

Function

Alternate Function

LCAS

Output

Column address strobe signal output for DRAM’s lower data

P90/LWR

UCAS

Output

Column address strobe signal output for DRAM’s higher data

P91/UWR

RAS3

P83/CS3

RAS4

P84/CS4/IOWR

RAS5

Output

Row address strobe signal output for DRAM

P85/CS5/IORD

BCYST

Output

Strobe signal output indicating start of bus cycle

P94

CS0

P80

CS3

P83/RAS3

CS4

P84/RAS4/IOWR

CS5

Output

Chip select signal output

P85/RAS5/IORD

WAIT

Input

Control signal input for inserting waits in bus cycle

PX6

IOWR

Output

DMA write strobe signal output

P84/RAS4/CS4

IORD

Output

DMA read strobe signal output

P85/RAS5/CS5

DMARQ0 to

DMARQ3

Input

DMA request signal input

P04/INTP100 to

P07/INTP103

DMAAK0 to

DMAAK3

Output

DMA acknowledge signal output

P14/INTP110 to

P17/INTP113

HLDAK

Output

Bus hold acknowledge output

P96

HLDRQ

Input

Bus hold request input

P97

ANI0 to ANI3

Input

Analog input to A/D converter

P70 to P73

NMI

Input

Non-maskable interrupt request input

P20

CLKOUT

Output

System clock output

PX7

CKSEL

Input

Input for specifying clock generator’s operation mode

–

MODE0,

MODE2

Input

Specify operation modes

–

RESET

Input

System reset input

–

X1

Input

–

X2

–

Connecting resonator for system clock. Input is via X1 when using an

external clock.

–

AV

REF

Input

Reference voltage input for A/D converter

–

AV

DD

–

Positive power supply for A/D converter

–

AV

SS

–

Ground potential for A/D converter

–

CV

DD

–

Positive power supply for dedicated clock generator

–

CV

SS

–

Ground potential for dedicated clock generator

–

V

DD

–

Positive power supply (power supply for internal units)

–

HV

DD

–

Positive power supply (power supply for external pins)

–

V

SS

–

Ground potential

–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD703130 | MOS INTEGRATED CIRCUIT |

| UPD703201 | 32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703204 | 32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD70F30025AGC-25 | LJT 24C 12#16 12#12 PIN PLUG |

| UPD70F3004AGC-33 | 32-bit RISC Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD703131A | 制造商:NEC 制造商全稱:NEC 功能描述:32-Bit Single-Chip Microcontrollers |

| UPD703131AF1-EN4 | 制造商:NEC 制造商全稱:NEC 功能描述:32-Bit Single-Chip Microcontrollers |

| UPD703131AF1-XXX-EN4 | 制造商:NEC 制造商全稱:NEC 功能描述:32-Bit Single-Chip Microcontrollers |

| UPD703131AGJ-XXX-UEN | 制造商:NEC 制造商全稱:NEC 功能描述:32-Bit Single-Chip Microcontrollers |

| UPD703131AY | 制造商:NEC 制造商全稱:NEC 功能描述:32-Bit Single-Chip Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。