- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382628 > TMP320F2812GHHS (Texas Instruments, Inc.) DIGITAL SIGNAL PROCESSORS PDF資料下載

參數(shù)資料

| 型號(hào): | TMP320F2812GHHS |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | DIGITAL SIGNAL PROCESSORS |

| 中文描述: | 數(shù)字信號(hào)處理器 |

| 文件頁數(shù): | 107/147頁 |

| 文件大小: | 2021K |

| 代理商: | TMP320F2812GHHS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁當(dāng)前第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁

E

1

S

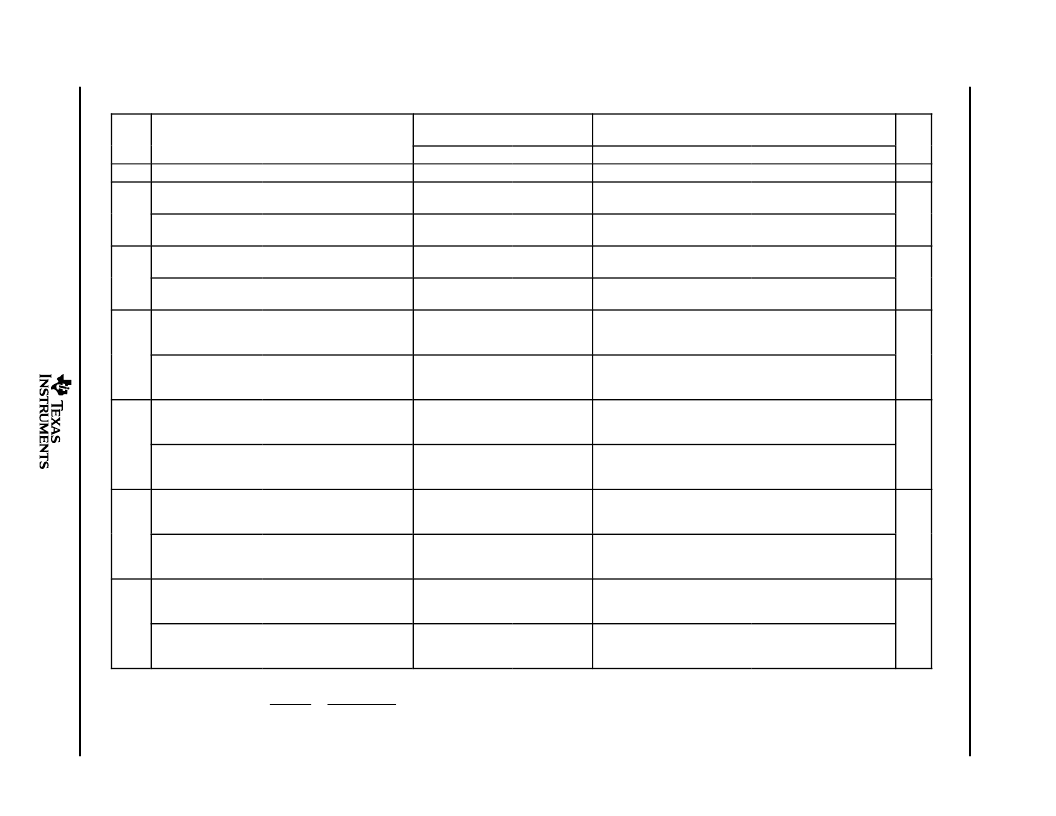

Table 6

21. SPI Master Mode External Timing (Clock Phase = 1)

NO.

SPI WHEN (SPIBRR + 1) IS EVEN

OR SPIBRR = 0 OR 2

SPI WHEN (SPIBRR + 1)

IS ODD AND SPIBRR > 3

UNIT

MIN

MAX

128t

c(LCO)

MIN

MAX

1

t

c(SPC)M

Cycle time, SPICLK

Pulse duration, SPICLK high

(clock polarity = 0)

4t

5t

c(LCO)

127t

c(LCO)

ns

2

§

t

w(SPCH)M

0.5t

c(SPC)M

10

0.5t

c(SPC)M

0.5t

c(SPC)M

0.5t

c(LCO)

10

0.5t

c(SPC)M

0.5t

c(LCO)

ns

t

w(SPCL)M

Pulse duration, SPICLK low

(clock polarity = 1)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

0.5t

c(SPC)M

0.5t

c(LCO)

10

0.5t

c(SPC)M

0.5t

c(LCO)

3

§

t

w(SPCL)M

Pulse duration, SPICLK low

(clock polarity = 0)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

0.5t

c(SPC)M

+0.5t

c(LCO)

10

0.5t

c(SPC)M

+ 0.5t

c(LCO)

ns

t

w(SPCH)M

Pulse duration, SPICLK high

(clock polarity = 1)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

0.5t

c(SPC)M

+0.5t

c(LCO)

10

0.5t

c(SPC)M

+ 0.5t

c(LCO)

6

§

t

su(SIMO-SPCH)M

Setup time, SPISIMO data

valid before SPICLK high

(clock polarity = 0)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

10

ns

t

su(SIMO-SPCL)M

Setup time, SPISIMO data

valid before SPICLK low

(clock polarity = 1)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

10

7

§

t

v(SPCH-SIMO)M

Valid time, SPISIMO data

valid after SPICLK high

(clock polarity = 0)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

10

ns

t

v(SPCL-SIMO)M

Valid time, SPISIMO data

valid after SPICLK low

(clock polarity = 1)

0.5t

c(SPC)M

10

0.5t

c(SPC)M

10

10

§

t

su(SOMI-SPCH)M

Setup time, SPISOMI before

SPICLK high

(clock polarity = 0)

0

0

ns

t

su(SOMI-SPCL)M

Setup time, SPISOMI before

SPICLK low

(clock polarity = 1)

0

0

11

§

t

v(SPCH-SOMI)M

Valid time, SPISOMI data

valid after SPICLK high

(clock polarity = 0)

Valid time, SPISOMI data

valid after SPICLK low

(clock polarity = 1)

0.25t

c(SPC)M

10

0.5t

c(SPC)M

10

ns

t

v(SPCL-SOMI)M

0.25t

c(SPC)M

10

0.5t

c(SPC)M

10

The MASTER/SLAVE bit (SPICTL.2) is set and the CLOCK PHASE bit (SPICTL.3) is set.

t

c(SPC)

= SPI clock cycle time = LS4

t

c(LCO)

= LSPCLK cycle time

§

The active edge of the SPICLK signal referenced is controlled by the CLOCK POLARITY bit (SPICCR.6).

NOTE: Internal clock prescalers must be adjusted such that the SPI clock speed is not greater than the I/O buffer speed limit (20 MHz).

or

LSPCLK

(SPIBRR

1)

ADVANCE INFORMATION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMP320F2812PBKA | DIGITAL SIGNAL PROCESSORS |

| TMX320R2811ZHHA | TOOL ALIGNMNT FLAT BLAD CRMC 2.6 |

| TMP320F2812ZHHA | TOOL ALIGNMENT PHILIPS CRMC 4IN1 |

| TMP320C2811ZHHA | TWEEZER P3C VERY FINE STR TIPS |

| TMR320F2812ZHHA | MAGNIFIER W/CURVED TWEEZER TIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320F2812PBKA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMP320F2812PBKQ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMP320F2812PBKS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMP320F2812PGFA | 制造商:Texas Instruments 功能描述:DSP FIX PT 32BIT 150MHZ 150MIPS 176LQFP - Trays |

| TMP320F2812PGFMEP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Signal Processors |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。