- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383960 > TMP320C6411ZLZ (Texas Instruments, Inc.) FIXED POINT DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | TMP320C6411ZLZ |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 定點(diǎn)數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 109/119頁(yè) |

| 文件大小: | 1742K |

| 代理商: | TMP320C6411ZLZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)當(dāng)前第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)

SPRS196H MARCH 2002 REVISED JULY 2004

109

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

MULTICHANNEL BUFFERED SERIAL PORT (McBSP) TIMING (CONTINUED)

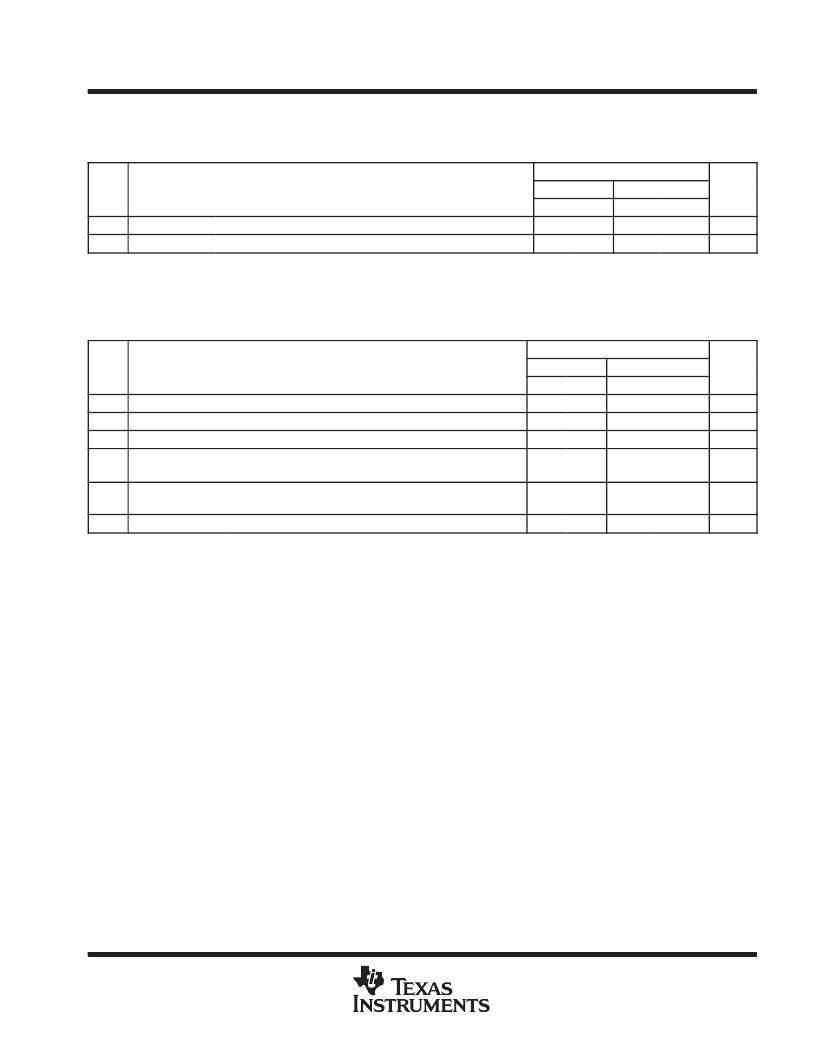

timing requirements for McBSP as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1

(see Figure 55)

300

NO.

MASTER

MIN

SLAVE

MIN

UNIT

MAX

MAX

4

tsu(DRV-CKXH)

th(CKXH-DRV)

Setup time, DR valid before CLKX high

12

2 12P

ns

5

Hold time, DR valid after CLKX high

4

5 + 24P

ns

P = 1/CPU clock frequency in ns. For example, when running parts at 300 MHz, use P = 3.33 ns.

For all SPI Slave modes, CLKG is programmed as 1/4 of the CPU clock by setting CLKSM = CLKGDV = 1.

switching characteristics over recommended operating conditions for McBSP as SPI Master or

Slave: CLKSTP = 10b, CLKXP = 1

(see Figure 55)

300

NO.

PARAMETER

MASTER§

SLAVE

UNIT

MIN

MAX

MIN

MAX

1

th(CKXH-FXL)

td(FXL-CKXL)

td(CKXL-DXV)

Hold time, FSX low after CLKX high

Delay time, FSX low to CLKX low#

T 2

T + 3

ns

2

H 2

H + 3

ns

3

Delay time, CLKX low to DX valid

2

4

12P + 4

20P + 17

ns

6

tdis(CKXH-DXHZ)

Disable time, DX high impedance following last data bit from

CLKX high

H 2

H + 3

ns

7

tdis(FXH-DXHZ)

Disable time, DX high impedance following last data bit from

FSX high

4P + 3

12P + 17

ns

8

td(FXL-DXV)

Delay time, FSX low to DX valid

8P + 2

16P + 17

ns

P = 1/CPU clock frequency in ns. For example, when running parts at 300 MHz, use P = 3.33 ns.

For all SPI Slave modes, CLKG is programmed as 1/4 of the CPU clock by setting CLKSM = CLKGDV = 1.

§S =

Sample rate generator input clock = 4P if CLKSM = 1 (P = 1/CPU clock frequency)

=

Sample rate generator input clock = P_clks if CLKSM = 0 (P_clks = CLKS period)

T =

CLKX period = (1 + CLKGDV) * S

H =

CLKX high pulse width = (CLKGDV/2 + 1) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

L =

CLKX low pulse width

= (CLKGDV/2) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

FSRP = FSXP = 1. As a SPI Master, FSX is inverted to provide active-low slave-enable output. As a Slave, the active-low signal input on FSX

and FSR is inverted before being used internally.

CLKXM = FSXM = 1, CLKRM = FSRM = 0 for Master McBSP

CLKXM = CLKRM = FSXM = FSRM = 0 for Slave McBSP

#FSX should be low before the rising edge of clock to enable Slave devices and then begin a SPI transfer at the rising edge of the Master clock

(CLKX).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX32C6411ZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMP32C6411AGLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMP32C6411GLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMX32C6411GLZ | Anti-Static Storage Bags; External Height:5"; External Width:3"; Thickness:0.12" |

| TMP320C6411GLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320C6411ZLZ300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411ZLZ5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411ZLZA300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411ZLZA5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6413GTS400 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processors |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。