- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383960 > TMP320C6411GLZ (Texas Instruments, Inc.) FIXED POINT DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | TMP320C6411GLZ |

| 廠商: | Texas Instruments, Inc. |

| 元件分類(lèi): | 數(shù)字信號(hào)處理 |

| 英文描述: | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 定點(diǎn)數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 38/119頁(yè) |

| 文件大小: | 1742K |

| 代理商: | TMP320C6411GLZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)

SPRS196H MARCH 2002 REVISED JULY 2004

38

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

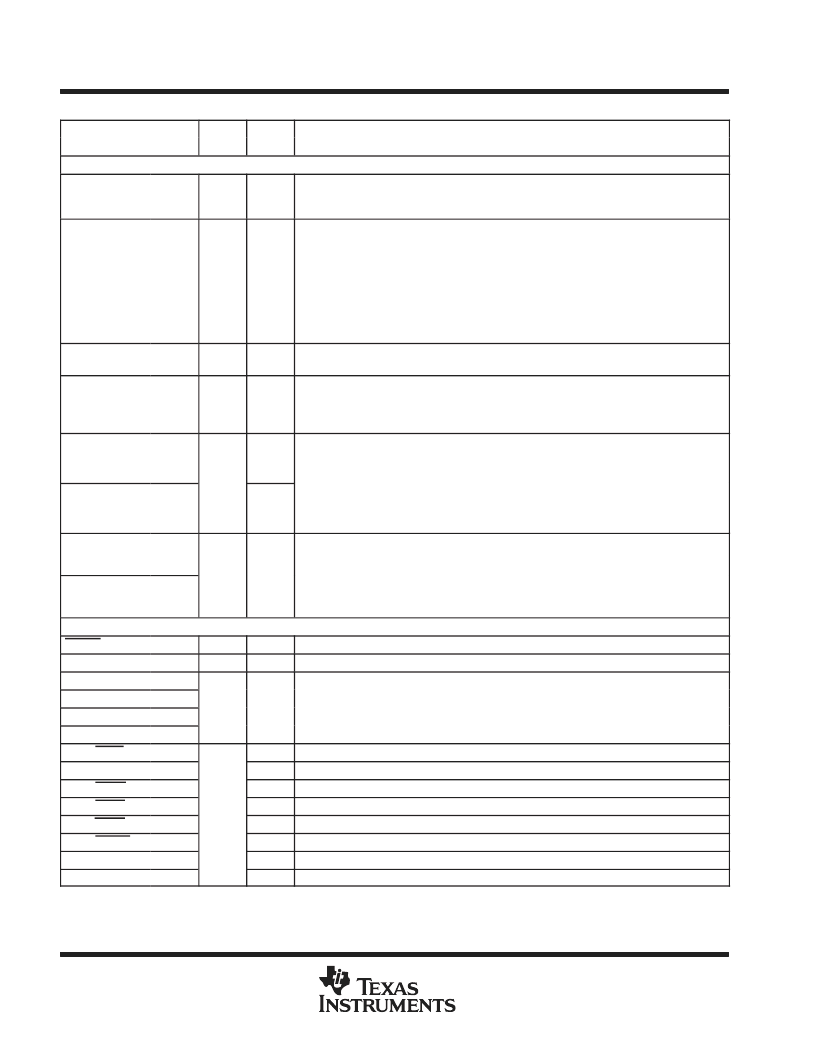

Terminal Functions (Continued)

SIGNAL

TYPE

IPD/

IPU

DESCRIPTION

NAME

NO.

DEVICE CONFIGURATION

LEND

E16

I/O/Z

IPU

Device Endian mode

LEND:

0

1

–

Big Endian

Little Endian (default mode)

HD5/AD5§

Y1

I/O/Z

Host-Port bus width (HPI_WIDTH) user-configurable at device reset via a 10-k

resistor

pullup/pulldown resistor on the HD5 pin:

HD5 pin = 0: HPI operates as an HPI16.

(HPI bus is 16 bits wide. HD[15:0] pins are used and the remaining HD[31:16] pins are

reserved pins in the high-impedance state.)

HD5 pin = 1: HPI operates as an HPI32.

(HPI bus is 32 bits wide. All HD[31:0] pins are used for host-port operations.)

PCI_EN

AA4

I

IPD

PCI enable pin. This pin controls the selection (enable/disable) of the HPI and GP[15:9], or

PCI peripherals. For more details, see the Device Configurations section of this data sheet.

EEAI

B17

I/O/Z

IPD

PCI EEPROM Auto-Initialization (EEAI) via external EEPROM

If

the PCI peripheral is disabled (PCI_EN pin = 0), this pin must

not

be pulled up.

EEAI: 0

PCI auto-initialization through EEPROM is disabled (default).

1

PCI auto-initialization through EEPROM is enabled.

BOOTMODE1

D18

I/O/Z

IPU

Boot mode. Default is reserved. External pullup and/or pulldown resistors must be used to

select a valid bootmode configuration.

BOOTMODE[1:0]:

00 –

01

10

11

No boot

HPI boot

Reserved

EMIF 8-bit ROM boot with default timings (default mode)

BOOTMODE0

C18

IPD

ECLKIN_SEL1

B18

I/O/Z

IPD

EMIF clock mode select

ECLKIN_SEL[1:0]: 00 –

ECLKIN (default mode)

CPU/4 Clock Rate

CPU/6 Clock Rate

Reserved

ECLKIN_SEL0

A18

01

10

11

RESETS, INTERRUPTS, AND GENERAL-PURPOSE INPUT/OUTPUTS

RESET

AC7

I

Device reset

NMI

B4

I

IPD

Nonmaskable interrupt, edge-driven (rising edge)

GP7/EXT_INT7

AF4

General-purpose input/output (GPIO) pins (

I/O/Z

) or external interrupts (

input only

). The

default after reset setting is GPIO enabled as input-only.

When these pins function as External Interrupts [by selecting the corresponding interrupt

enable register bit (IER.[7:4])], they are edge-driven and the polarity can be independently

selected via the External Interrupt Polarity Register bits (EXTPOL.[3:0]).

General-purpose input/output (GPIO) 15 pin (

I/O/Z

) or PCI reset (

I

). No function at default.

GPIO 14 pin (

I/O/Z

) or PCI clock (

I

). No function at default.

GPIO 13 pin (

I/O/Z

) or PCI interrupt A (

O/Z

). No function at default.

GPIO 12 pin (

I/O/Z

) or PCI bus grant (

I

). No function at default.

GPIO 11 pin (

I/O/Z

) or PCI bus request (

O/Z

). No function at default.

GPIO 10 pin (

I/O/Z

) or PCI command/byte enable 3 (

I/O/Z

). No function at default.

GPIO 9 pin (

I/O/Z

) or PCI initialization device select (

I

). No function at default.

GPIO 3 pin (

I/O/Z

).

GP6/EXT_INT6

AD5

I/O/Z

IPU

GP5/EXT_INT5

AE5

GP4/EXT_INT4

GP15/PRST§

GP14/PCLK§

GP13/PINTA§

GP12/PGNT§

GP11/PREQ§

GP10/PCBE3§

GP9/PIDSEL§

AF5

G3

F2

G4

J3

I/O/Z

F1

L2

M3

GP3

I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground

IPD = Internal pulldown, IPU = Internal pullup. (These IPD/IPU signal pins feature a 30-k

IPD or IPU resistor. To pull up a signal to the opposite

supply rail, a 1-k

resistor should be used, unless otherwise noted.)

§These pins are multiplexed pins. For more details, see the Device Configurations section of this data sheet.

AC6

IPD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMP470R1B768PGE | 16/32-Bit RISC Flash Microcontroller |

| TMP47C020 | Transient Voltage Suppressor Diodes |

| TMP47C020G | Transient Voltage Suppressor Diodes |

| TMP47C050 | Transient Voltage Suppressor Diodes |

| TMP47C050E | Transient Voltage Suppressor Diodes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP320C6411GLZ300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411GLZ5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411GLZA300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411GLZA5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6411ZLZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED POINT DIGITAL SIGNAL PROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。