- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98229 > THS8083-95CPZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | THS8083-95CPZP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | POWER, THERMALLY ENHANCED, PLASTIC, TQFP-100 |

| 文件頁(yè)數(shù): | 9/61頁(yè) |

| 文件大小: | 239K |

| 代理商: | THS8083-95CPZP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

2–3

Ext. Logic

PFD_FREEZE

CS

THS8083

HS

Frame Period

PFD_FREEZE High in VBI on Lines Where CS

Has Multiple Rising/Falling Edges Per Line

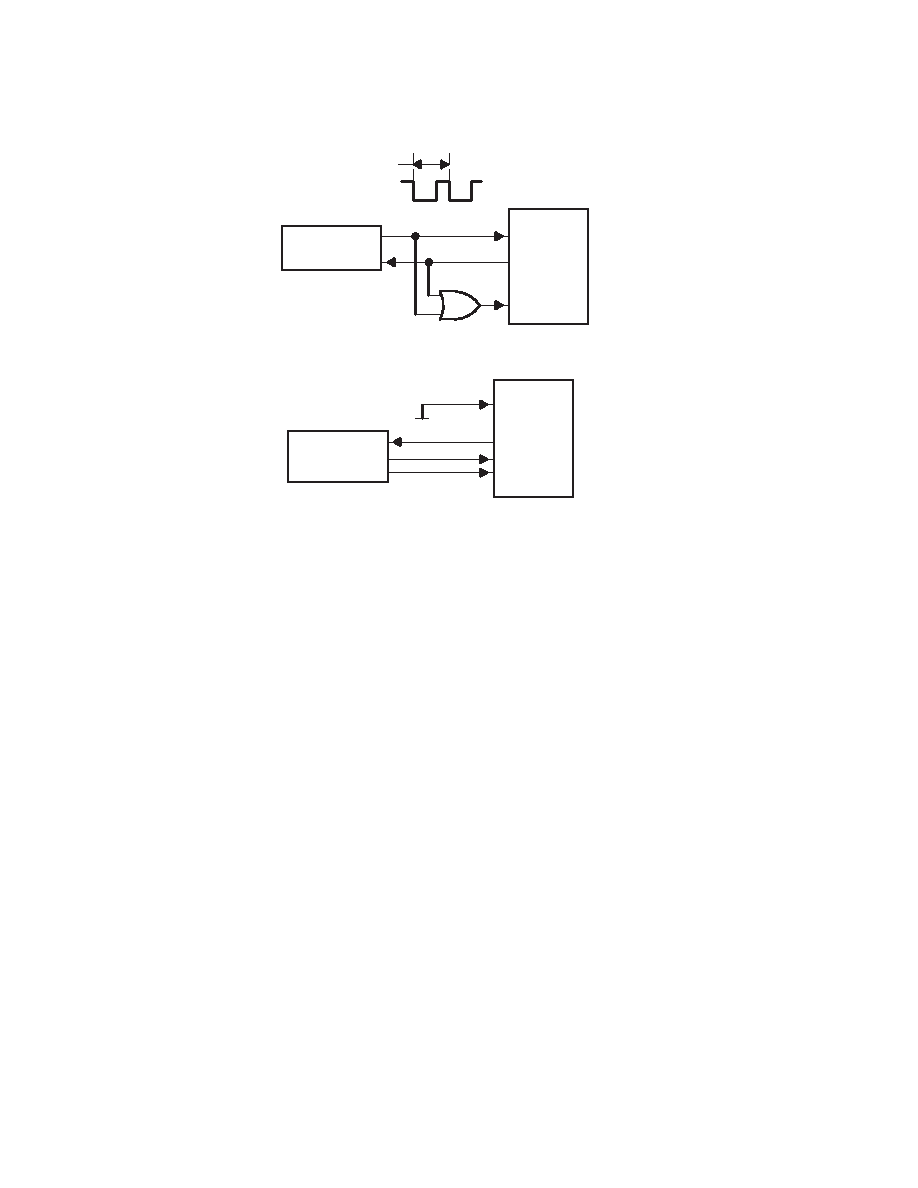

Option 1: Using PFD_FREEZE

Sync.

Separator

CS

THS8083

HS

Option 2: Using HS Derived From CS

PFD_FREEZE

VS

Figure 2–4. Using THS8083 With a Composite Sync

Note that the slicer will only work when no video levels are lower than the blanking level and when the internal clamp

circuit is used. This is normally satisfied for G and Y channels, but not for U and V channels. To prevent unnecessary

toggling of the CS output signal, the CS output is switched off automatically when mid-level clamping is chosen for

channel 1 (i.e., CLP1_RG=1 in register <CLP_CTRL>). CS can be permanently disabled by setting CS_DIS=1 in

register <AUX_CTRL>. So the state of CS is determined as follows:

CS_ENABLED = NOT (CS_DIS) AND NOT (CLP1_RG).

When CS_ENABLED=0, the CS output will be Hi-Z.

NOTE:

While PFD_FREEZE keeps the DTO output frequency constant, it does not disable the

phase/frequency detector (PFD) from internally updating its error value at every active edge

on HS. Therefore, when deasserting PFD_FREEZE and no external sync separator is used,

a discontinuity on the frequency increment to the DTO occurs which will cause an

instantaneous frequency shift. To prevent this, the user should gate the CS signal externally

with the PFD_FREEZE signal as shown in Figure 2.4. This will keep the PFD from updating

during PFD_FREEZE high, since HS will remain low during the VBI. By using both

PFD_FREEZE and gating during the vertical blanking interval, THS8083 can be locked to

signals with a composite sync.

To support sync-on-Y/sync-on-G extraction, the user should provide an external dc biasing to

the Y/G channel. This can be done by establishing a dc clamp through a diode with its cathode

connected to the ac-coupling capacitor (at the side of THS8083) on the AGY channel and

anode connected to a dc level. Since the slicing level is around 1.35 V and the sync amplitude

is ~300 mV, the negative sync-tip should be clamped by the diode to a level of approximately

1.2 V. For example, using a Schottky switching diode (type 1N5711) with a low forward voltage

drop of maximum 0.4 V, the dc level at the anode can be approximately 1.6 V. This level can

be derived through a resistive voltage divider off the power supply.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS8083APZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8083APZPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8083CPZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8133ACPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS8083A | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:TRIPLE 8 BIT 80 MSPS 3.3V VIDEO AND GRAPHICS |

| THS8083A95 | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:TRIPLE 8-BIT, 95MSPS, 3.3V VIDEO AND GRAPHICS |

| THS8083A95PZP | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 Tr 8B 95MSPS 3.3V Vid & Graphics Dig RoHS:否 制造商:Texas Instruments 輸入信號(hào)類(lèi)型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類(lèi)型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| THS8083APZP | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 Triple 8B 80 MSPS 3.3V YUV/RGB RoHS:否 制造商:Texas Instruments 輸入信號(hào)類(lèi)型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類(lèi)型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| THS8083APZP | 制造商:Texas Instruments 功能描述:8BIT ADC 80MSPS TRIPLE SMD 8083 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。