- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98211 > TEF6892H/V2,518 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | TEF6892H/V2,518 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封裝: | 10 X 10 MM, 1.75 MM HEIGHT, PLASTIC, SOT-307-2, QFP-44 |

| 文件頁數(shù): | 25/59頁 |

| 文件大?。?/td> | 329K |

| 代理商: | TEF6892H/V2,518 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

2003 Oct 21

31

Philips Semiconductors

Product specication

Car radio integrated signal processor

TEF6892H

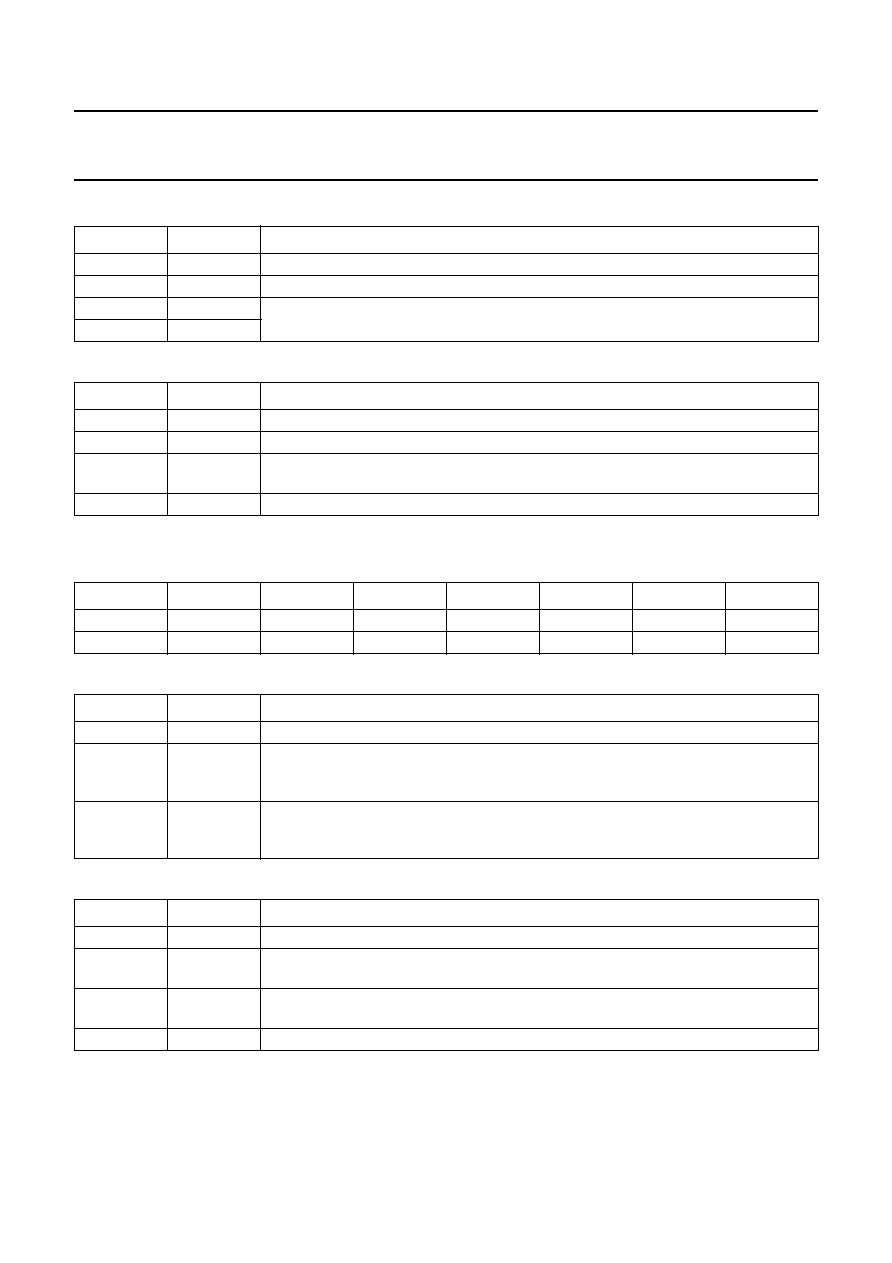

Table 36 Description of data byte 2H

Table 37 RDS clock description

11.2.4

SUBADDRESS 3H; RDS CONTROL

Table 38 Format of data byte 3H with default setting

Table 39 Description of data byte 3H

Table 40 Description of data available control

BIT

SYMBOL

DESCRIPTION

7 and 6

Not used. Set to logic 0.

5 to 2

TST[3:0]

Test. TST[3:0] = 0000: normal operation.

1

CLKO

Clock input or output and buffered or unbuffered raw RDS output. See Table 37.

0

CLKI

CLKO

CLKI

RDS/RBDS CLOCK

0

RDS decoder mode; pin RDCL is disabled

0

1

for RDS decoder bypass mode; RDCL is burst clock input for raw RDS read-out

1

0

for RDS decoder mode: continuous block rate data available signal at pin RDCL;

for RDS decoder bypass mode: RDCL is clock output for raw RDS read-out

1

reserved

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

DAC1

DAC0

NWSY

BBG4

BBG3

BBG2

BBG1

BBG0

00000000

BIT

SYMBOL

DESCRIPTION

7 and 6

DAC[1:0]

Data available control. See Table 40.

5

NWSY

New synchronization search. 0 = synchronization is started by BBL value of bad block

counter only; 1 = restart of synchronization search. NWSY is automatically reset to

logic 0.

4 to 0

BBG[4:0]

Maximum bad blocks gain. Number of invalid blocks (bad block counter) that is

allowed during synchronization search. If reached, a new synchronization is started.

BBG[4:0] = 0 disables this function.

DAC1

DAC0

DATA AVAILABLE CONTROL

0

standard output mode; new block data is signalled at every new received block

0

1

fast PI search mode; during synchronization search (SYNC = 0) A or C’ block data is

available and signalled, when synchronized standard output mode is active

1

0

reduced data request mode; when synchronized new block data is signalled every two

new received blocks

1

decoder bypass mode; raw RDS data from demodulator is available on pin RDDA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TEF6892H/V2,557 | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| TEF6894H/V2,518 | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| TEF6894H | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| TEL4935-2G | SPECIALTY ANALOG CIRCUIT, PSSO3 |

| TEL4905G | SPECIALTY ANALOG CIRCUIT, PSSO3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TEF6894H/V2,518 | 功能描述:音頻 DSP ANALOG SIGNAL PROCESSOR RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TEF6894H/V3 | 功能描述:音頻 DSP ANALOG SGNL PROCESSR RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TEF6894H/V3,518 | 功能描述:音頻 DSP ANALOG SGNL PROCESSR RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TEF6894H/V3,557 | 功能描述:音頻 DSP ANALOG SGNL PROCESSR RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TEF6894H/V3-T | 功能描述:音頻 DSP ANALOG SGNL PROCESSR RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。