- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98211 > TEA6822T-T (NXP SEMICONDUCTORS) AM/FM, AUDIO SINGLE CHIP RECEIVER, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | TEA6822T-T |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 接收器 |

| 英文描述: | AM/FM, AUDIO SINGLE CHIP RECEIVER, PDSO56 |

| 封裝: | PLASTIC, SOT-190-1, VSOP-56 |

| 文件頁數(shù): | 20/48頁 |

| 文件大?。?/td> | 351K |

| 代理商: | TEA6822T-T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

1997 Feb 12

27

Philips Semiconductors

Preliminary specication

In Car Entertainment (ICE) car radio

TEA6820T; TEA6822T

I2C-BUS AND I2C-BUS CONTROLLED FUNCTIONS

I2C-bus specication

The standard I2C-bus specification is expanded by the

following definitions.

Structure of the I2C-bus logic: slave transceiver with auto

increment and expansion to switch a direct transfer of all

transmissions to an output for the radio front-end IC

(TEA6810T respectively TEA6811T).

Subaddresses are not used.

DATA TRANSFER FOR THE TEA6820T AND THE TEA6822T

Data sequence:

Address

Byte 1

Byte 2.

The data transfer maybe in this order only. The transfer

direction of the data bytes is defined by the LSB of the

address.

The data becomes valid at the output of the internal

latches with the acknowledge of each byte. A STOP

condition after any byte can shorten transmission times.

When writing to the transceiver by using the STOP

condition before completion of the whole transfer:

The remaining bytes will contain the old information

If the transfer of a byte was not completed, this byte is

lost and the previous information is available.

DATA TRANSFER TO AN OUTPUT OF THE FRONT-END IC

A data bit in the transceiver of the TEA6820T or TEA6822T

enables or disables a direct transfer of all transmissions to

an interface stage for the front-end IC.

For a transmission to the front-end IC the address and the

data format of the front-end IC has to be used.

Remark: the pull-up resistors for the front-end interface

(pins 6 and 7) should not be connected to the 5 V supply

voltage of the front-end IC, otherwise a bus pull-down

(pin 53) can occur during switching off the front-end supply

when the interface stage is enabled.

DATA TRANSFER TO THE IF IC

Data transfer to the IF IC (TEA6820T or TEA6822T) is

independent of the state of interface stage for the front-end

IC.

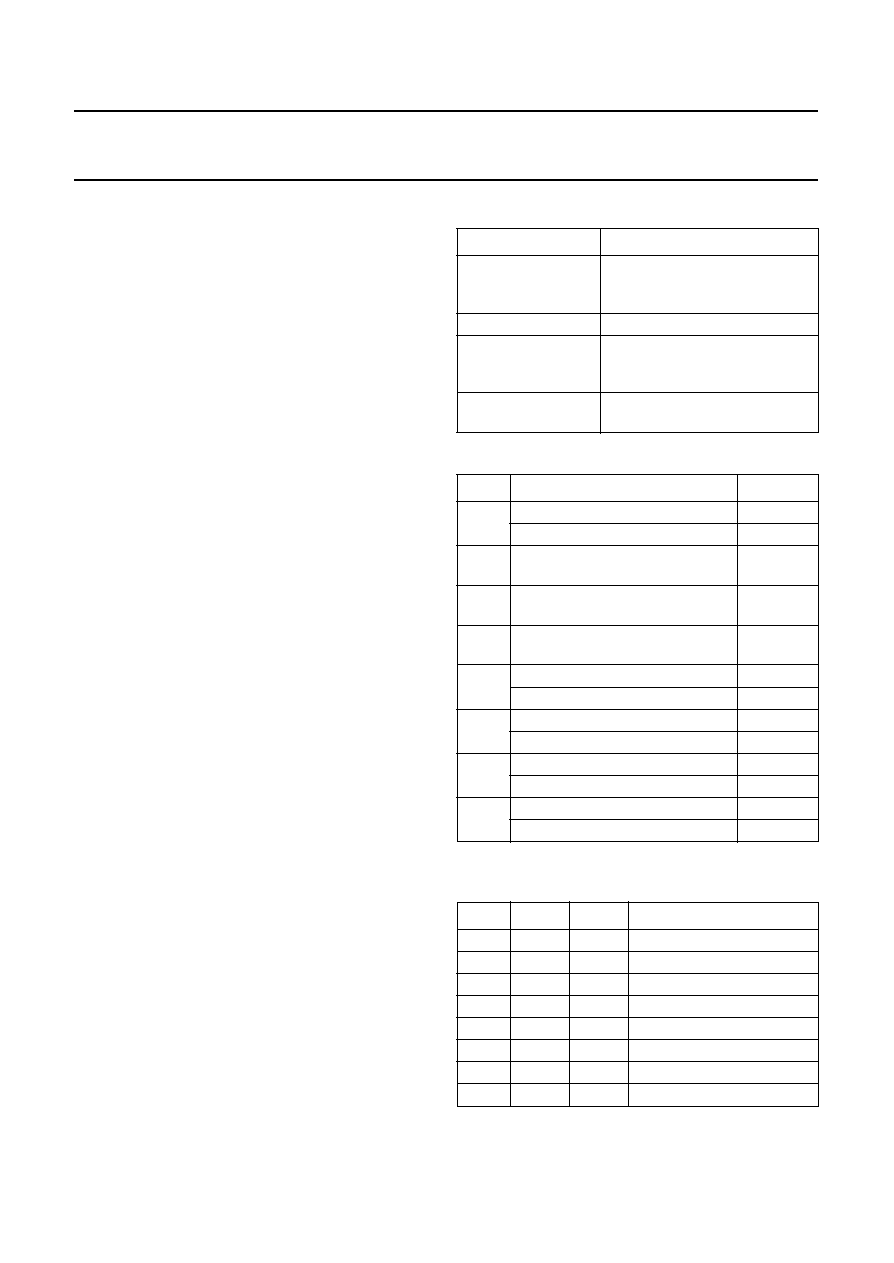

Table 1

Structure of the I2C-bus

Table 2

Data to be received by the IC for data byte 1

Table 3

Reference frequency setting in data byte 1;

see Table 1

DESCRIPTION

SPECIFICATION

Bus address of the

TEA6820T and the

TEA6822T

1100001X

Subaddress

not used

Hardware (pin)

programmable

address bits

not available

Default settings by

power-on reset

data byte 1 bits 4 to 7 are set to

logic ‘0’; all other bits are random

BIT

DESCRIPTION

RESULT

0

switch for mono

bit0=1

switch for stereo

bit0=0

1

LSB reference frequency for

synthesizer

2

reference frequency for

synthesizer

3

MSB reference frequency for

synthesizer

4

tuning mute off

bit4=1

tuning mute on

bit4=0

5

SDS/SDR hold off

bit5=1

SDS/SDR hold on

bit5=0

6

radio mute off

bit6=1

radio mute on

bit6=0

7I2C-bus to front-end ENABLED

bit7=1

I2C-bus to front-end DISABLED

bit7=0

BIT 3

BIT 2

BIT 1

FREQUENCY SETTING

0

3 kHz

0

1

5 kHz

0

1

0

10 kHz

0

1

15 kHz

1

0

25 kHz

1

0

1

50 kHz

1

0

not dened

1

not dened

相關PDF資料 |

PDF描述 |

|---|---|

| TEA6843HL/V1,518 | AM/FM, AUDIO SINGLE CHIP RECEIVER, PQFP80 |

| TEA7532DP | AUDIO AMPLIFIER, PDIP16 |

| TEA7532FP | AUDIO AMPLIFIER, PDSO16 |

| TEA7650H-T | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TEF6890H/V2,518 | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TEA6823 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:In Car Entertainment ICE car radio |

| TEA6823T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:In Car Entertainment ICE car radio |

| TEA6824 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:In Car Entertainment ICE car radio |

| TEA6824T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:In Car Entertainment ICE car radio |

| TEA6825 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:In Car Entertainment ICE car radio |

發(fā)布緊急采購,3分鐘左右您將得到回復。