- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98174 > TC7109CPL 1-CH 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PDIP40 PDF資料下載

參數(shù)資料

| 型號: | TC7109CPL |

| 元件分類: | ADC |

| 英文描述: | 1-CH 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PDIP40 |

| 封裝: | PLASTIC, DIP-40 |

| 文件頁數(shù): | 9/30頁 |

| 文件大小: | 479K |

| 代理商: | TC7109CPL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

2006 Microchip Technology Inc.

DS21456C-page 17

TC7109/A

4.0

INTERFACING

4.1

Direct Mode

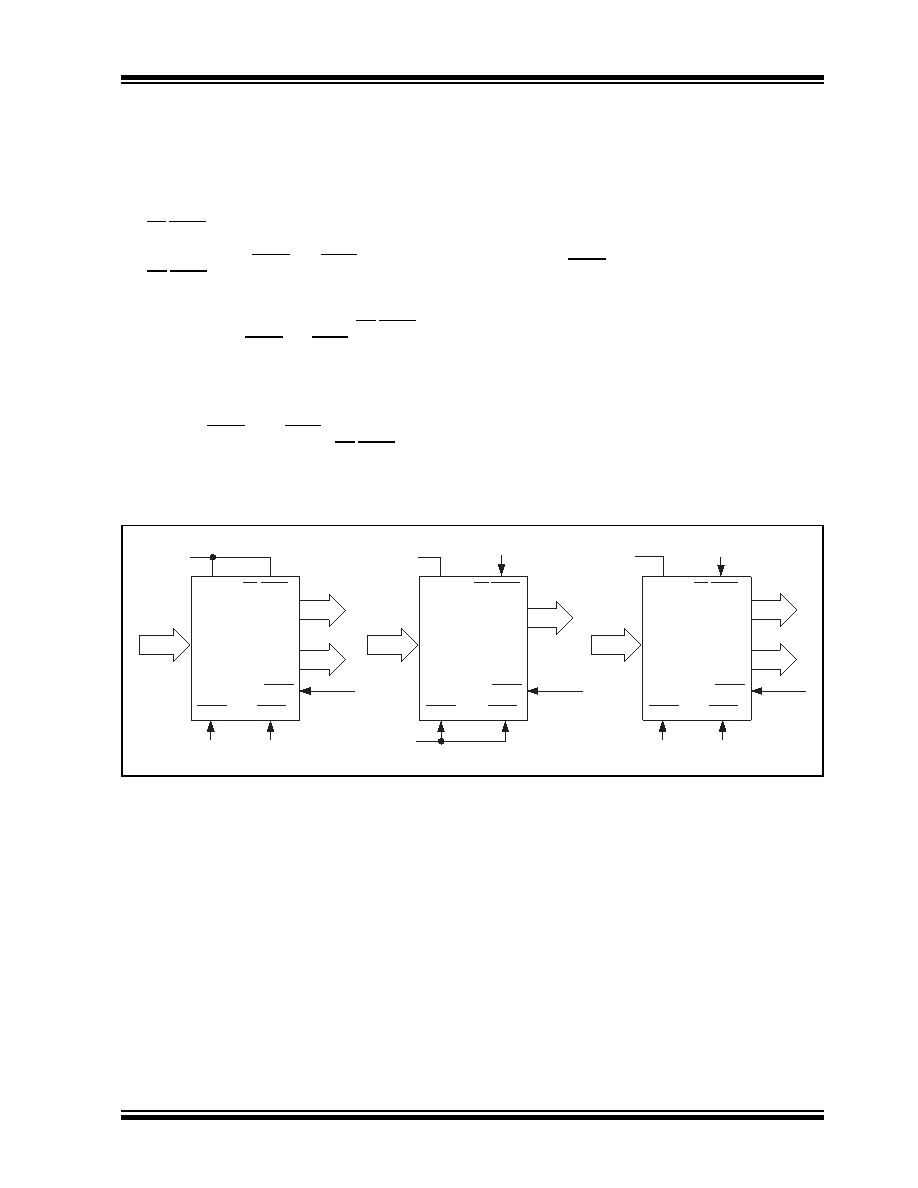

Combinations of chip enable and byte enable control

signals, which may be used when interfacing the

TC7109A to parallel data lines, are shown in Figure .

The CE/LOAD input may be tied low, allowing either byte

to be controlled by its own enable (see Figure (A)).

Figure (B) shows the HBEN and LBEN as flag inputs,

and CE/LOAD as a master enable, which could be the

READ strobe available from most microprocessors.

Figure (C) shows a configuration where the two byte

enables are connected together. The CE/LOAD is a

chip enable, and the HBEN and LBEN may be used as

a second chip enable, or connected to ground. The 14

data outputs will be enabled at the same time. In the

direct MODE, SEND should be tied to V+.

Figure shows interfacing several TC7109A’s to a bus,

ganging the HBEN and LBEN signals to several

converters together, and using the CE/LOAD input to

select the desired converter.

the parallel three-state output capabilities of the

TC7109A. Figure shows parallel interface to the 8748/

49 systems via an 8255 PPI, where the TC7109A data

outputs are active at all times. This interface can be

used in a read-after-update sequence, as shown in

Figure . The data is accessed by the high-to-low

transition of the Status driving an interrupt to the

microcontroller.

The RUN/HOLD

input is

also used to initiate

conversions under software control.

Direct interfacing to most microcontroller busses is

easily accomplished through the three-state output of

the TC7109A.

Figure 4-8 is a typical connection diagram. To ensure

requirements for setup and hold times, minimum pulse

widths, and the drive limitations on long busses are

met, it is necessary to carefully consider the system

timing in this type of interface. This type of interface is

used when the memory peripheral address density is

low, providing simple address decoding. Interrupt

handling can be simplified by using an interface to

reduce the component count.

FIGURE 4-1:

Direct Mode Chip and Byte Enable Combination

TC7109A

MODE

CE/LOAD

B9 - B12

POL, OR

B1 - B8

LBEN

HBEN

GND

8

Analog In

6

Convert

Control

RUN/HOLD

TC7109A

MODE

CE/LOAD

B1 - B12

POL, OR

LBEN

HBEN

GND

Analog In

Convert

RUN/HOLD

TC7109A

MODE

CE/LOAD

B9 - B12

POL, OR

B1 - B8

LBEN

HBEN

8

Analog In

6

Convert

RUN/HOLD

Chip Select 1

GND or

Chip Select 2

14

Byte Flags

GND

Chip Select

A.B.

C.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TC7109CLW713 | 1-CH 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PQCC44 |

| TC7109ACPL | 1-CH 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PDIP40 |

| TC7109CKW713 | 1-CH 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PQFP44 |

| TC7109ACKW | 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PQFP44 |

| TC7109ACPL | 12-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TC7109CPL | 制造商:Microchip Technology Inc 功能描述:IC 12BIT ADC 7109 DIP40 |

| TC7109CPL | 制造商:Microchip Technology Inc 功能描述:Special Function IC Package/Case:40-PDIP |

| TC7109IJL | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 13 Bit Fast Recovery RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TC7-10-C100 | 功能描述:電纜固定件和配件 CBL STRAP W/ TACK NAIL RoHS:否 制造商:Heyco 類型:Cable Grips, Liquid Tight 材料:Nylon 顏色:Black 安裝方法:Cable 最大光束直徑:11.4 mm 抗拉強度: |

| TC7110A | 制造商:Thomas & Betts 功能描述:Fittings Connector 4inch Steel |

發(fā)布緊急采購,3分鐘左右您將得到回復。